#### **VISUALSIM TRAINING**

### Agenda- Part 1: Basic Concepts

Overview

Areas of Modeling

Models of Computation

Modeling, Simulation, Analysis and Recommendation using VisualSim

Performance, Power and Functional Analysis

### Overview

# About Mirabilis Design

Started in 2007 and based in Santa Clara, CA, USA.

Development and support centers in US, India, Germany, China, Japan, Taiwan and Czech

System architecture exploration of electronics, semiconductors and software

Over 250 products worldwide across Semiconductors, Aerospace, Computing and Automotive

VisualSim- Modeling and simulation software

Largest source of system modeling IP with embedded timing and power

100's of man years experience in system design and exploration of digital electronics

### VisualSim Architect

- Graphical and Hierarchical modeling

- > Large library of parameterized components

- Integrated Discrete and Continuous Simulator

- Integrate API for simulators, programs and traces

- Optimizer to detect the best configuration

Comprehensive Architecture Exploration Solution

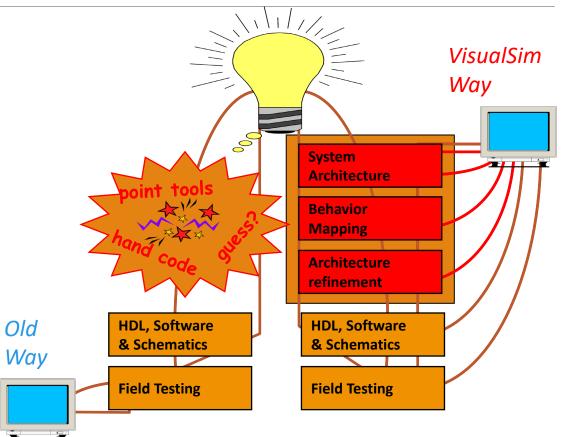

### Introduction to Conceptual Design

### "Is this the Right Design?"

- Translation from product concept to implementation is critical link

- Traditional methods are "ad-hoc"

- VisualSim approach reduces risk and speed's design

Errors in early stage cannot be rectified with optimized manufacturing

# WIRABLE Why is Architecture Exploration needed?

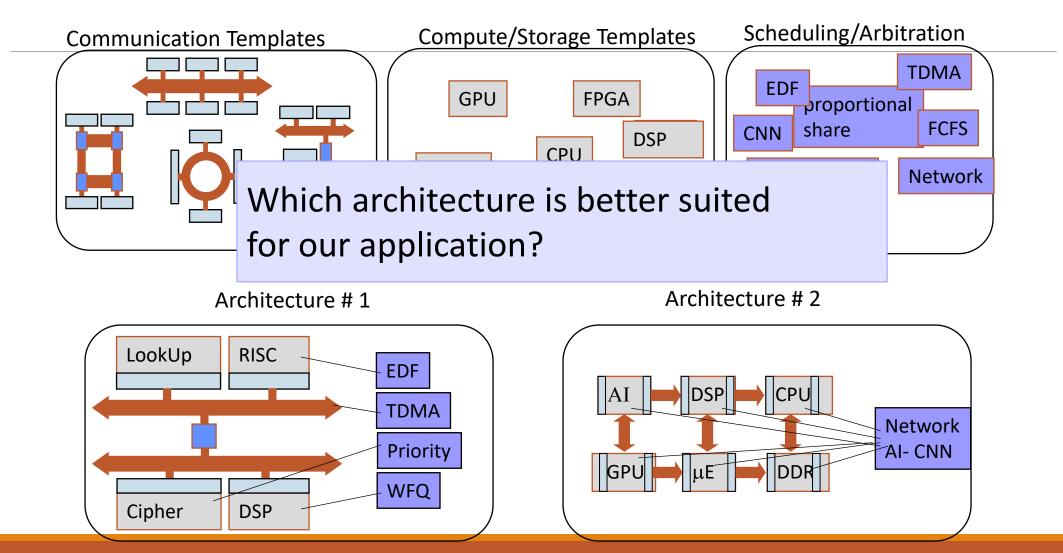

Run use-cases, workloads and traffic to decide on the best architecture

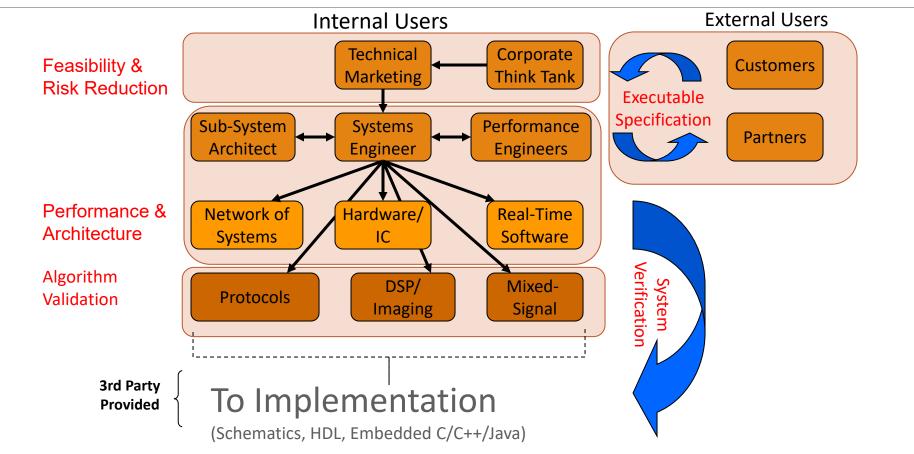

# Types of Model- For Architecture Exploration

#### Mission or Network level

- Flow model- xOn\_xOff.xml

- Network- demo/networking folder or demo/automotive

#### Full System including boards and boxes

- Embedded System- demo/System\_Architecture/Video\_Processing/Video\_Processing\_Model2.xml, demo/System\_Architecture/software\_Radar\_System/Large\_Radar\_System.xml. Demo/Bus\_Std/PCI\_Rad/ PCI\_RAD\_Demo.xml

- Software:demo/software\_devl/software\_methodology/Software\_tasks\_w\_Power.xml, demo/automotive/Autosar/AUTOSAR\_Scheduler/Autosar\_Model4a\_noCCode.xml

- Evaluating software code- demo/automotive/Autosar/AUTOSAR\_Scheduler/Autosar\_Model4a.xml (Requires compile)

#### SoC

- Hardware+Software- early exploration- Multi\_Core\_Soc\_V43.xml

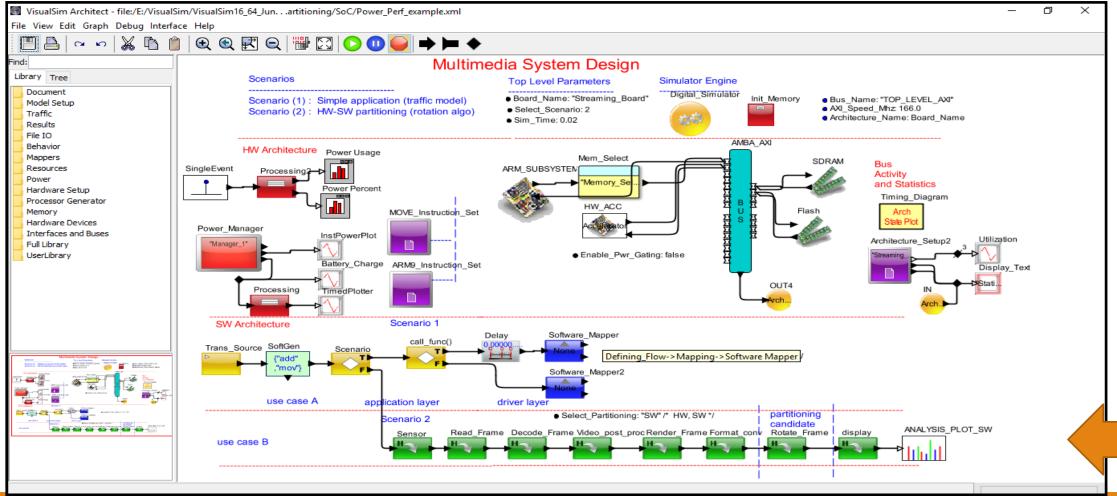

- Hardware+Software partitioning- Timing approximate- demo/partitioning/SoC/Power\_Perf\_Example.xml

- Hardware-software-cycle-accurate- CMN600\_with\_DDR5\_DynamicRT.xml

- Individual component- Bus and Memory-demo/complex\_system/Multi\_AXI\_to\_Memory\_Access.xml

### Complete Systems-Level Library

| <u>Traffic</u><br>Distribution<br>Sequence<br>Trace file<br>Instruction profile<br><u>Reports</u><br>Timing and Buffer<br>Throughput/Util<br>Ave/peak power<br>Statistics                                                                         | <ul> <li>Power</li> <li>State power table</li> <li>Power</li> <li>management</li> <li>Energy harvesters</li> <li>Battery</li> <li>RegEx operators</li> </ul>                                                                                                         | SoC Buses<br>AMBA and Corelink<br>AHB, AB, AXI, ACE,<br>CHI, CMN600<br>Network-on-Chip<br>TileLink                                                                                                                           | System Bus<br>PCI/PCI-X/PCIe<br>Rapid IO<br>AFDX<br>OpenVPX<br>VME<br>SPI 3.0<br>1553B                                                                                                                                                   | <ul> <li>Processors</li> <li>GPU, DSP, μP and μC</li> <li>RISC-V</li> <li>Nvidia- Drive-PX</li> <li>PowerPC</li> <li>X86- Intel and AMD</li> <li>DSP- TI and ADI</li> <li>MIPS, Tensilica, SH</li> </ul>                                                                                                                         | <b>ARM</b><br>• M-, R-, 7TDMI<br>• A8, A53, A55, A72,<br>A76, A77                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Custom Creator</li> <li>Script language</li> <li>600 RegEx fn</li> <li>Task graph</li> <li>Tracer</li> <li>C/C++/Java</li> <li>Python</li> <li>Support</li> <li>Listener and<br/>Trace</li> <li>Debuggers</li> <li>Assertions</li> </ul> | <ul> <li>Stochastic</li> <li>FIFO/LIFO Queue</li> <li>Time Queue</li> <li>Quantity Queue</li> <li>Quantity Queue</li> <li>System Resource</li> <li>Schedulers</li> <li>Cyber Security</li> <li>RTOS</li> <li>Template</li> <li>ARINC 653</li> <li>AUTOSAR</li> </ul> | Memory Controller <ul> <li>DDR DRAM 2,3,4, 5</li> <li>LPDDR 2, 3, 4</li> <li>HBM, HMC</li> <li>SDR, QDR, RDRAM</li> </ul> <li>Storage Array <ul> <li>Disk and SATA</li> <li>Fibre Channel</li> <li>FireWire</li> </ul> </li> | <ul> <li>Networking</li> <li>Ethernet &amp; GiE</li> <li>Audio-Video Bridging</li> <li>802.11 and Bluetooth</li> <li>5G</li> <li>Spacewire</li> <li>CAN-FD</li> <li>TTEthernet</li> <li>FlexRay</li> <li>TSN &amp; IEEE802.1Q</li> </ul> | <ul> <li>FPGA</li> <li>Xilinx- Zynq, Virtex, Kintex</li> <li>Intel-Stratix, Arria</li> <li>Microsemi- Smartfusion</li> <li>Programmable logic<br/>template</li> <li>Interface traffic generator</li> <li>Software code integration</li> <li>Instruction trace</li> <li>Statistical software model</li> <li>Task graph</li> </ul> | Interfaces<br>Virtual Channel<br>DMA<br>Crossbar<br>Serial Switch<br>Bridge<br><u>RTL-like</u><br>Clock, Wire-Delay<br>Registers, Latches<br>Flip-flop<br>ALU and FSM<br>Mux, DeMux<br>Lookup table |

Minimizes the need for custom development and quick custom development language

#

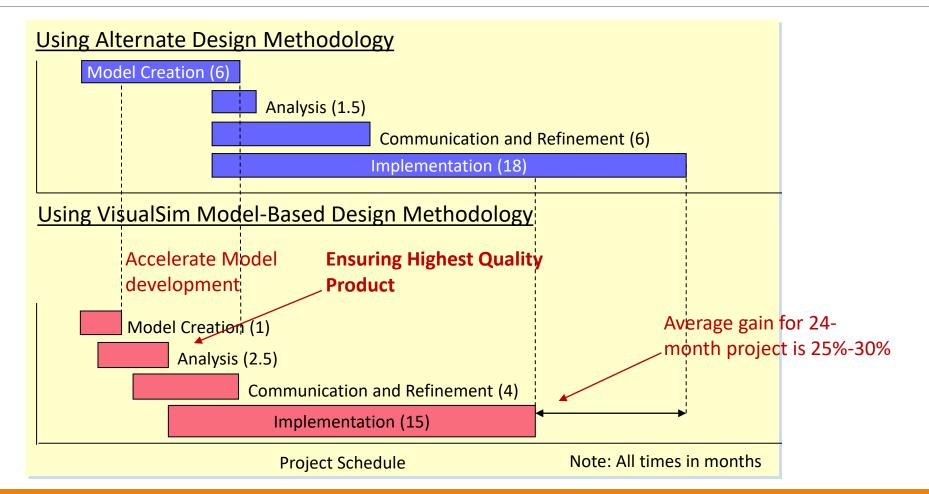

### Profit Upside using VisualSim

Quick Model Bring-UP and Meticulous Analysis

### Modeling Examples

### Modeling Examples

**Circuit and Mixed-Signal**

Traffic, Queueing, Flow Control and Stochastic

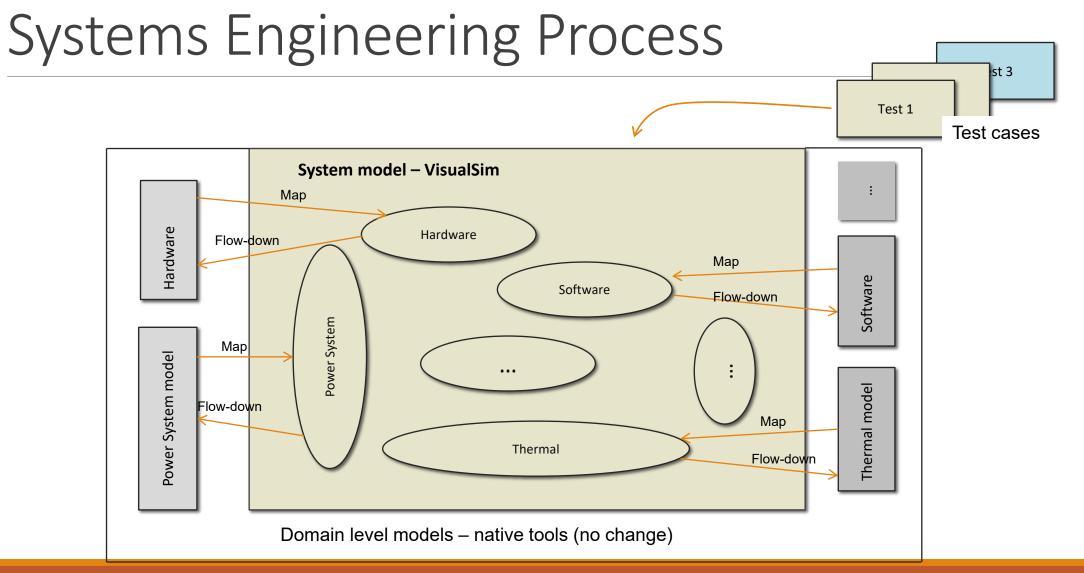

Systems Engineering Process

**Distributed Computing Systems**

Software Design

Sub-system

**FPGA Design**

Hardware-Software Partitioning

**Semiconductors**

#

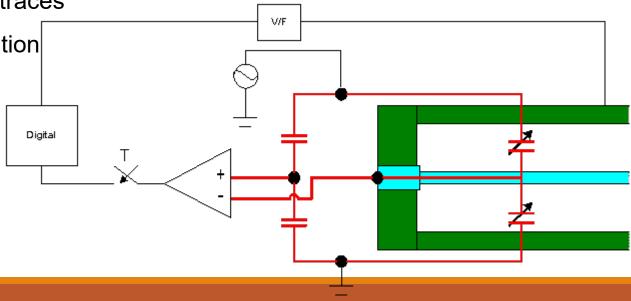

### Circuit Example

- Evaluate junctions and transistors

- Used to get global or system-wide perspective

- Semiconductor IC maybe a delay or a queue + processing element

- Traffic will be distribution-driven or network traces

- Traceability is the most important consideration

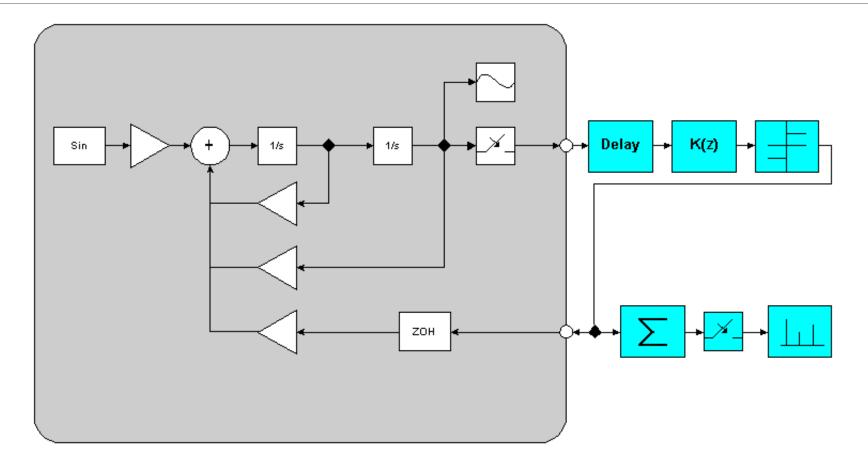

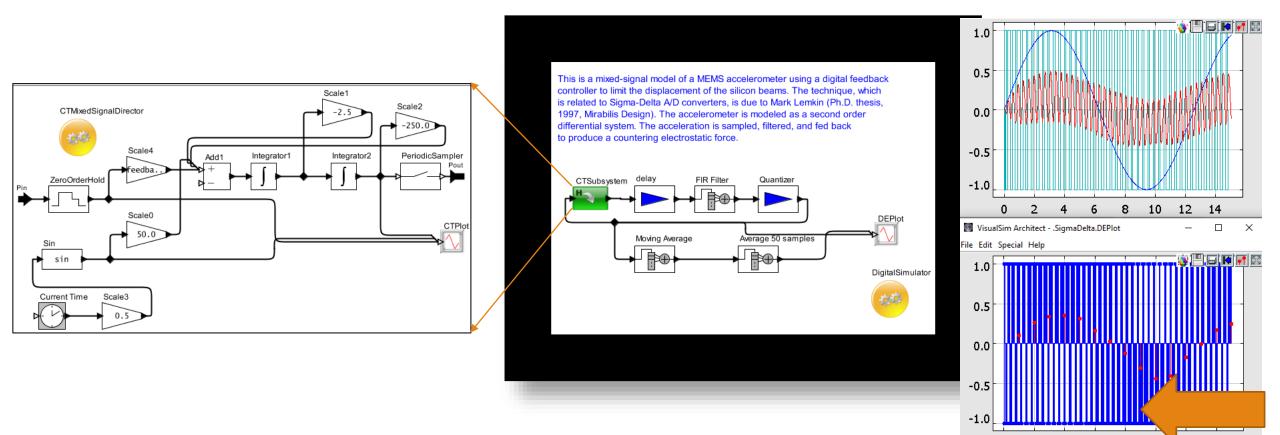

### Converting Sigma-Delta A/D to Behavioral Block Diagram

####

12 14

10

### Sigma-Delta A/D in VisualSim using Continuous and Discrete-Event SImulators

Focused on the correctness of the Mathematics. Similar to MatLab

#

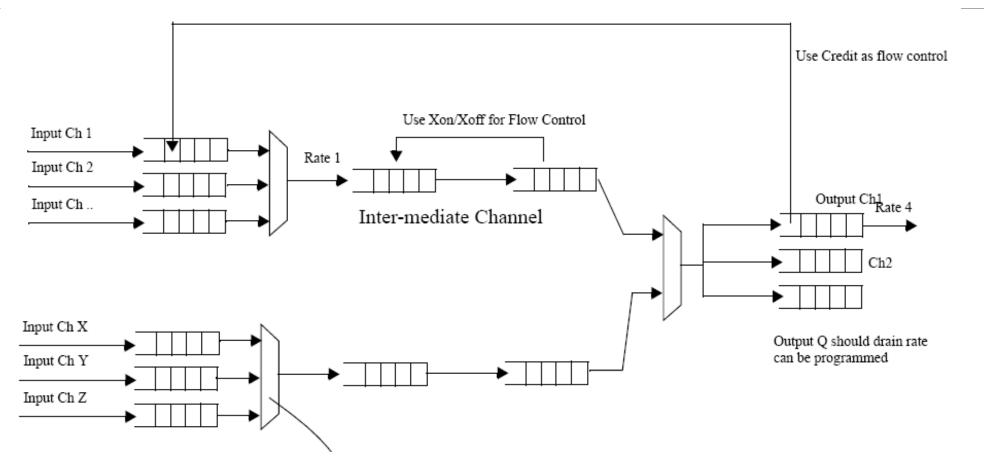

### Traffic or Queuing Analysis

#### Analysis

- Quick and extensive feasibility study

- Identify areas for detailed investigation

- Scheduling and priority analysis

#### Hardware

- Use a SystemResource to define each device

- Routing table to determine path for each task

#### Software

- · Generate a statistical profile for the software code to each target

- · Distribution-based traffic to emulate the task and message-passing

- · Add priority, target processor and task ordering

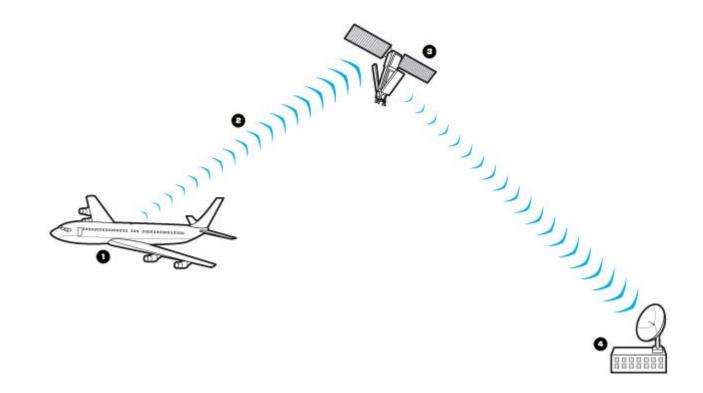

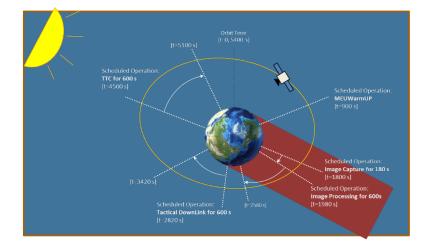

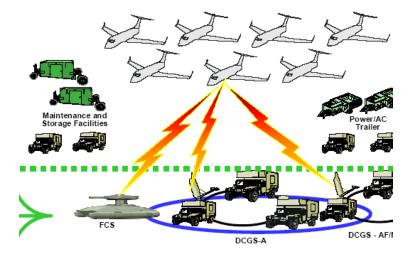

Throughput and feasibility study of Network of aircrafts, Ground Station and satellites

- Send and Receive data buffering, link margin and retransmission

- Size data packets to reduce power consumption for IoT devices

- Performance degradation due to retransmission or data loss

- Evaluate new protocol standards

- Exploring the impact of data center switches, bandwidth and routing paths

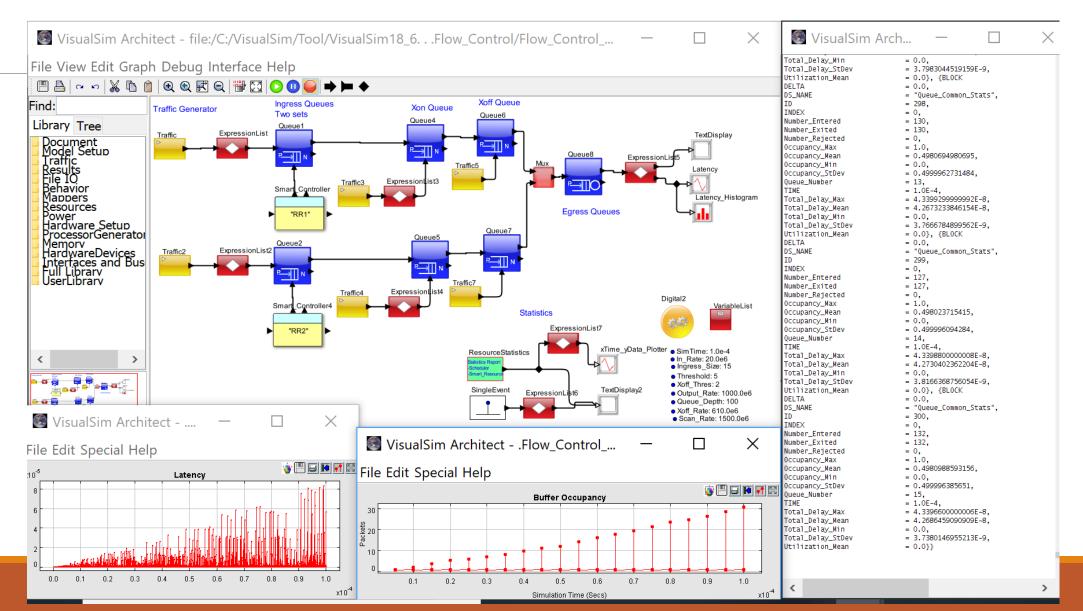

### Flow Control and Scheduling

### Modeling the Dynamic Behavior

MIRABI IS

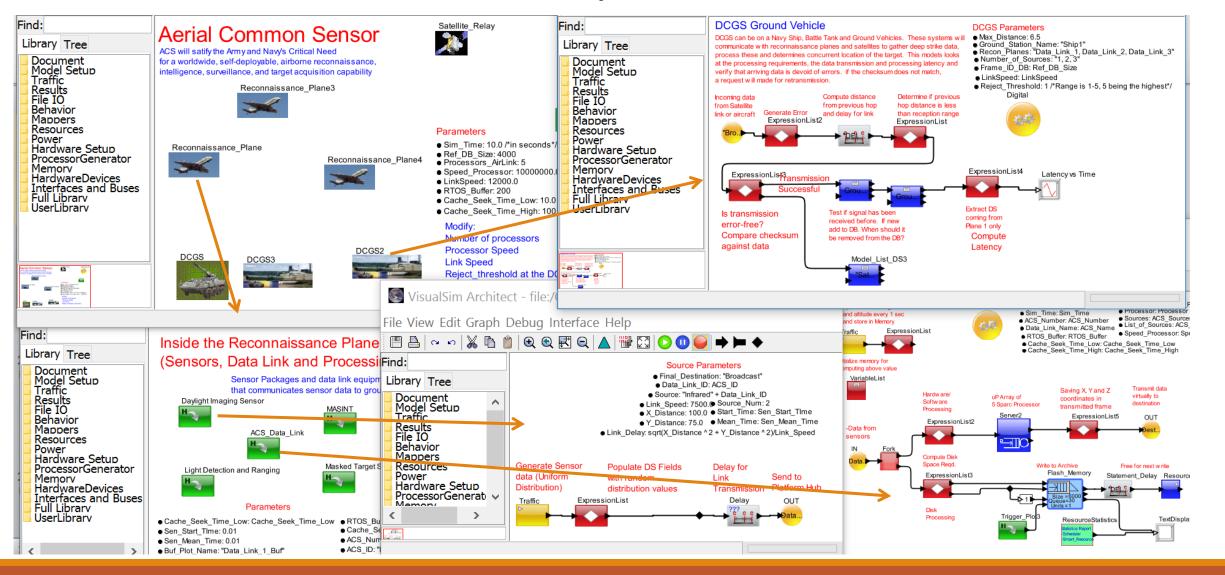

#### Traffic Engineering Example Top-Level of the Aerial System

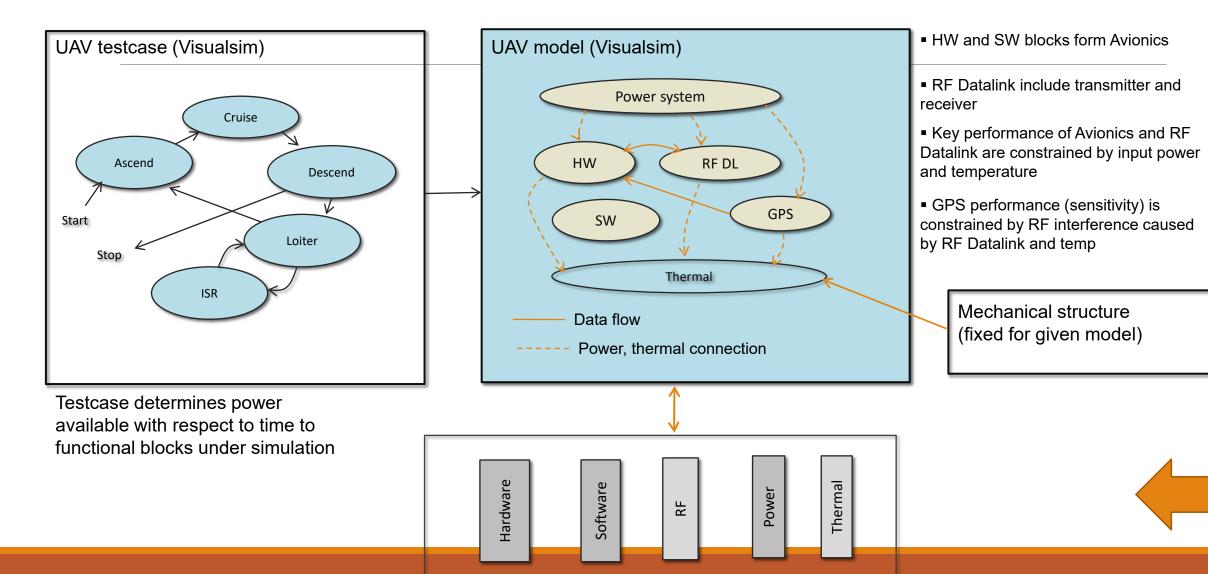

### **Mission-Level Analysis**

####

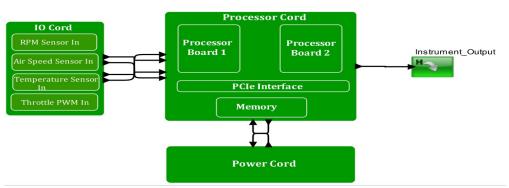

# End-Product Study Aerial Common Sensor- Challenges

How many sensor can the system handle?

Compute, Storage and Communication requirements

Timing and power consumption

Project scrapped?

• Weight and battery capacity issues

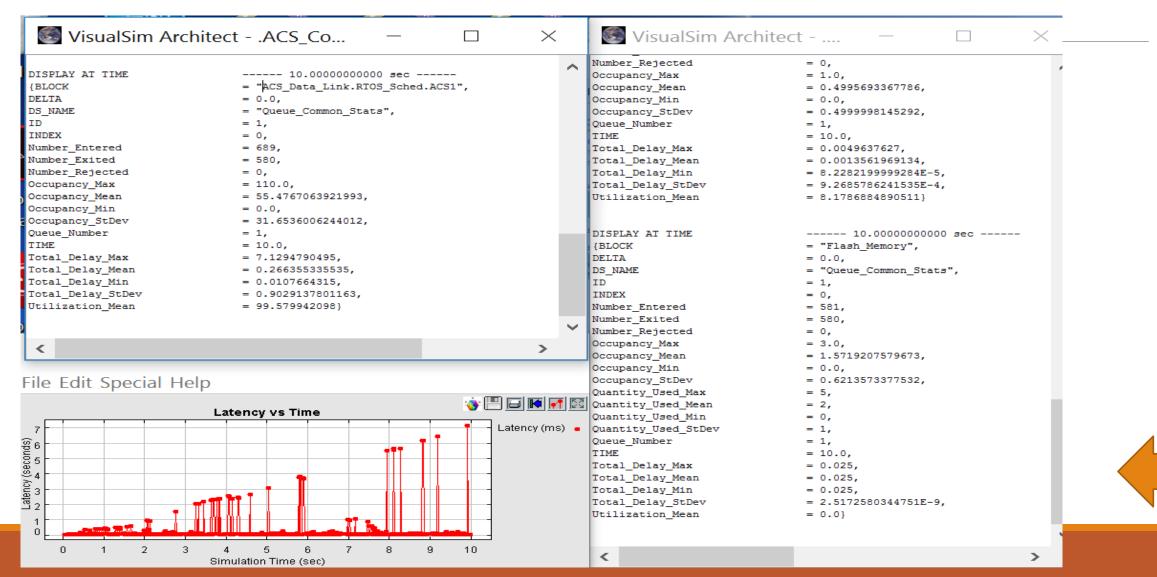

### End-Product Study

### Aerial Common Sensor

File View Edit Graph Debug Interface Help

####

### End-Product Study Aerial Common Sensor

VisualSim has capability to model most sub-systems/domains

### Aero Example

Domain level design

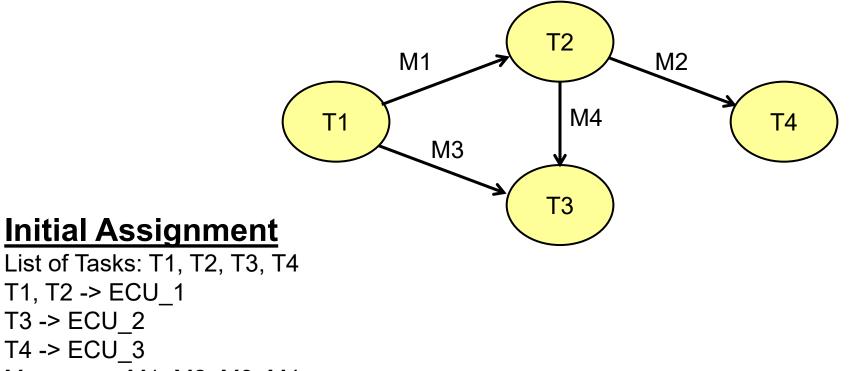

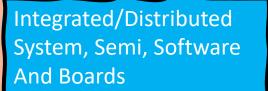

### Distributed System Analysis

### System details

- Multi-independent processing computers

- Software tasks distributed across these computers

- Connectivity across multiple shared networks

### Analysis

- Optimal Routing Table configuration

- Capacity planning

- Software tasks and thread distribution

- Resource allocation

### Distributed System Logical Task Flow

Messages: M1, M2, M3, M4

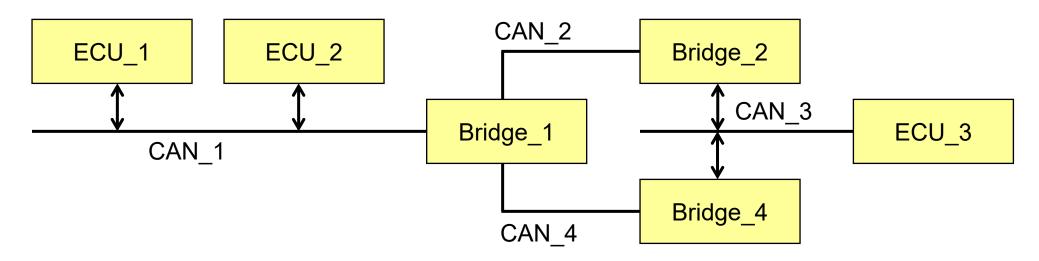

### Distributed System uP-Computer/Bus Physical Mapping

#### Message Assignment

•Messages: M1, M2, M3, M4

• Internal to ECU, if Source ECU == Destination ECU

•CAN\_N bus segments selection based on Source:Destination of Task,

- •Routing is selected for shortest hops

- •Dynamic allocation based on topology selection

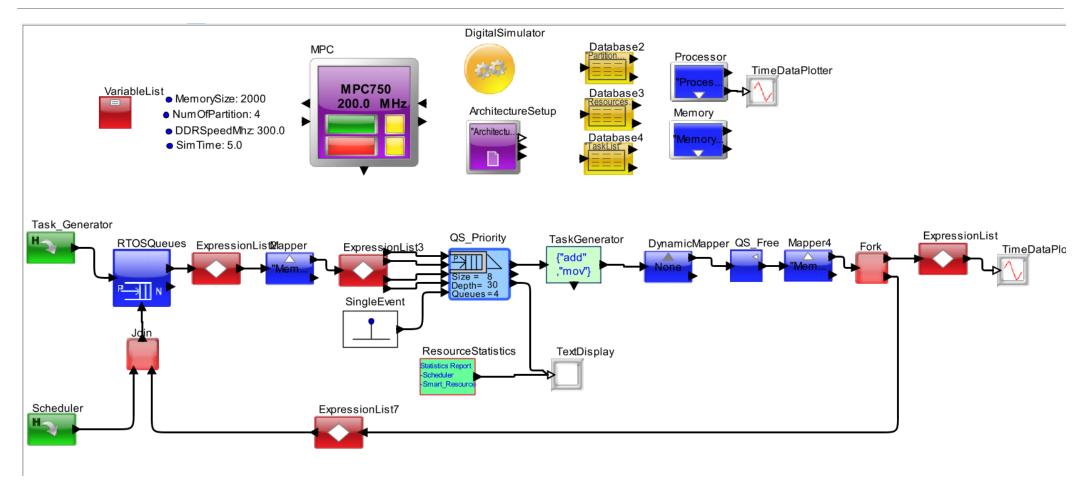

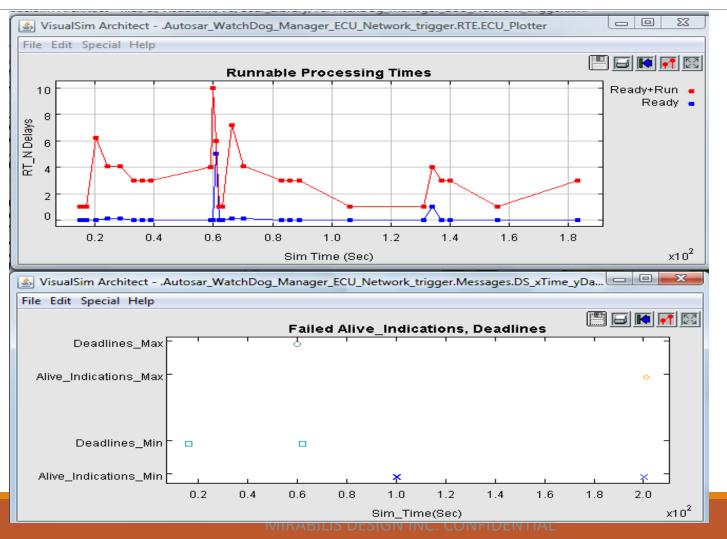

### Applications of VisualSim- Software

Software, RTOS and Scheduling

- Selecting the right scheduler and parameter definition

- Allocation of resources for the software task

- Validating the behavior of the security and safety features

- Parameter tuning or modifying software architecture

Exploring the Firmware

- Timing deadline for the firmware

- Power reduction techniques

- Validating correctness of the algorithm

- Allocating tasks across multi-core platforms

# Application Task Graph (Implementation can be in HW or SW)

#### Example

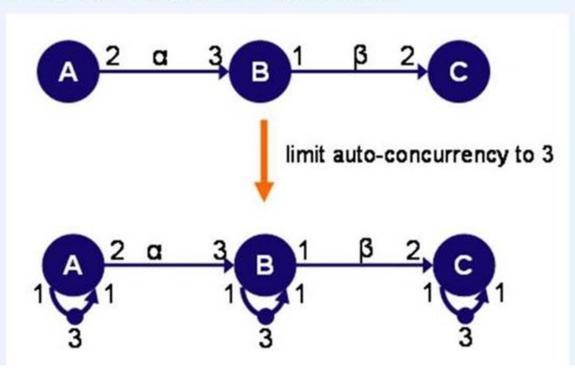

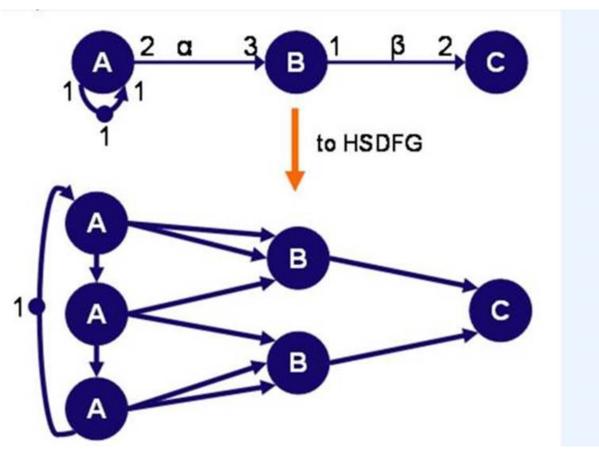

In this example, the auto-concurrency of the actors is limited to 3. This means that only three instances of each actor can be firing simultaneously.

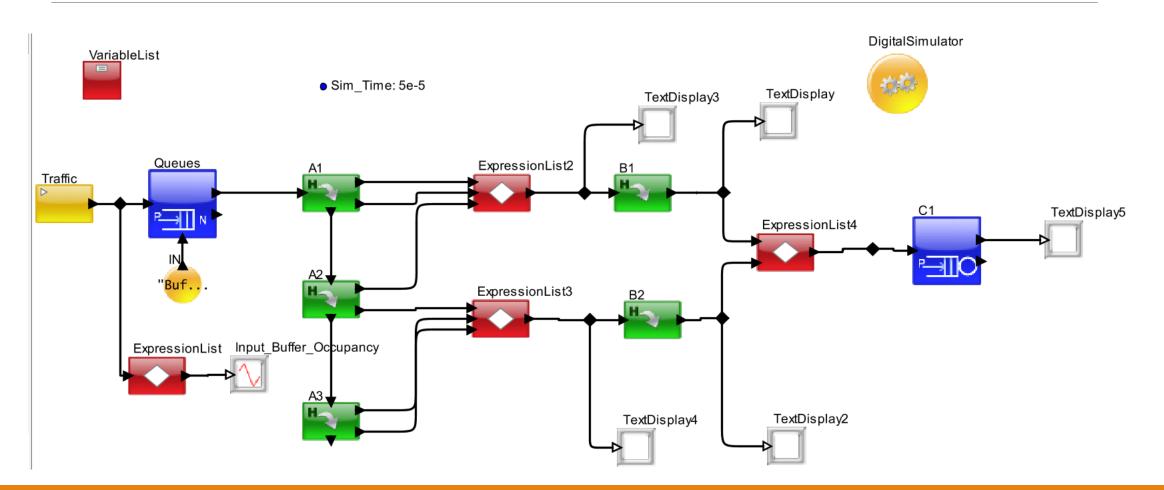

### VisualSim Model of the Task Graph

# Types of Exploration

- 1. Task Flow through system

- a. Source and intermediate nodes

- b. Latency for each flow per type

- c. Usage- processing, buses and memory

- 2. Loading on individual modules

- a. Memory throughput and consumption

- b. Bus and switch usage

- c. Failure and loss of data

- d. Non-availability of resources and memory

- b. Any starved flows

- 1. Task Flow internals

- a. Number of accesses per Node or Process

- b. Correctness of access

- c. Missing timing deadlines

- 2. Buffer and Scheduler

- a. Buffer size impacts

- b. Scheduler efficiency

- c. Waiting or stalled time

- d. Impact of task schedule offsets

####

### VisualSim Software Modeling- RAD750

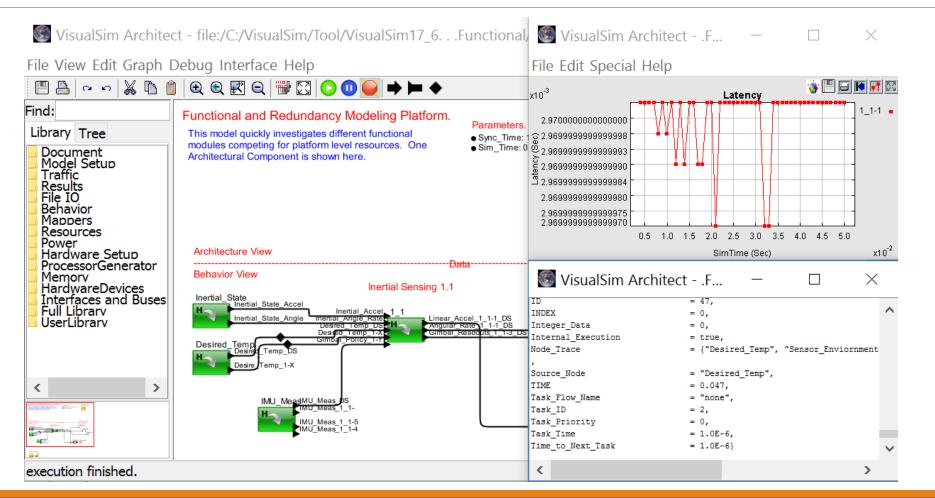

### VisualSim Latency and Functional Exploration Reports

MIRARI

8/8/2023

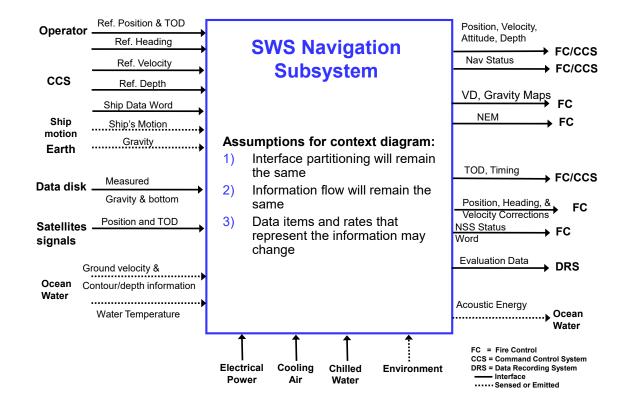

### Designing Sub-systems-Concept and Functional

### VisualSim Conceptual Model

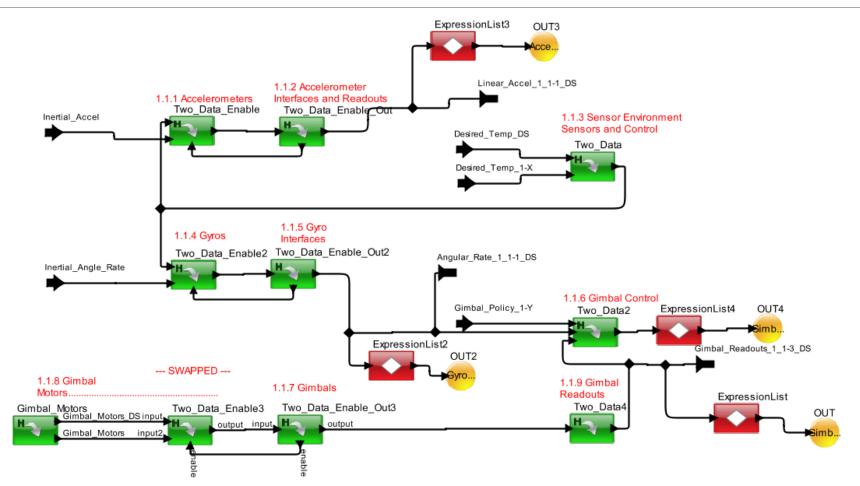

### View Internals of the Inertial Sensing

### Designing with FPGAs

Designers of FPGA systems can easily

- Profile interaction between multiple FPGA, Processors and external memory

- Improve product quality, performance, cost and power with accurate predictions

Eliminate performance bottlenecks with FPGA system models

- Accurate analysis of memory interfaces and processor-to-FPGA Fabric interconnect

- Easy task partitioning to μBlaze, PPC and hardware accelerators for best system performance

## Analysis using Xilinx Zynq-7000

Buffering, Latency and throughput statistics

- For all buses

- Minimum, maximum, and mean

- DMA I/Os per second

### Memory

- Number of Reads and Writes to Memory

- Effective throughput to Memory

### Processor

• Hit-ratio, pipeline throughput, buffering and memory required

### Hardware-Software Partitoning

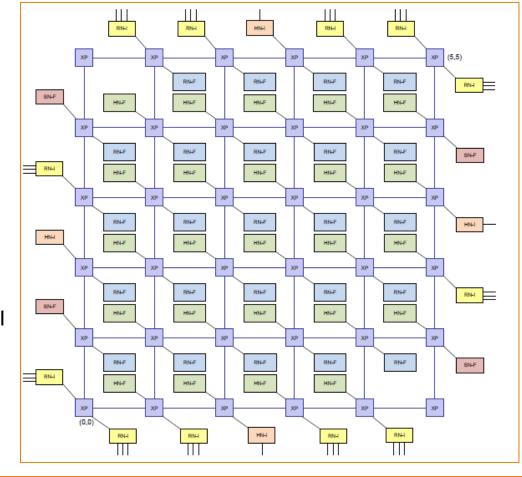

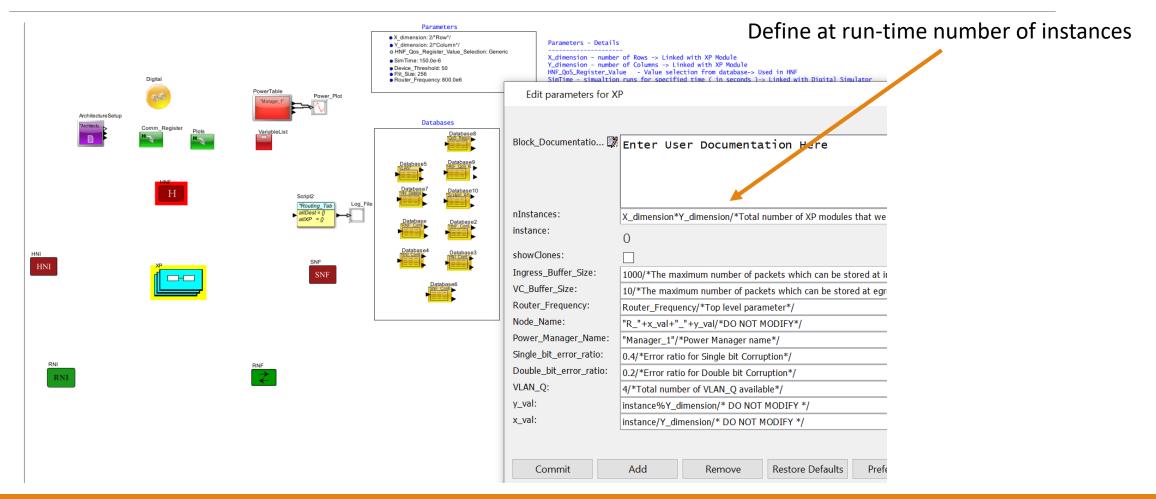

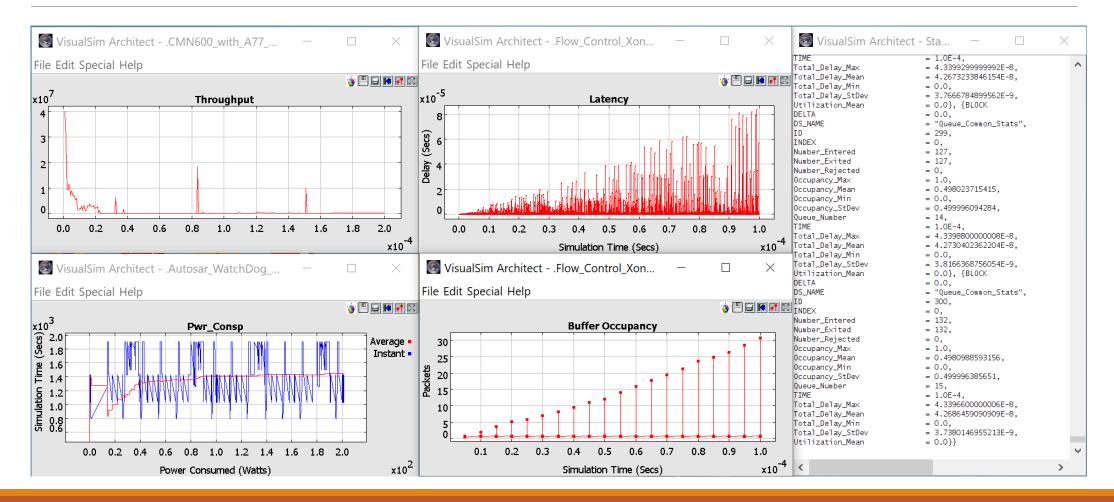

### Creating Extremely Large Systems

#### **Devices in the SoC**

CMN600 NoC 6\*6 and 8\*8 8 AI Processor Cores 64 ARM Z1 Cores 16 GPU 4 DRAM5 and 2 HBM2.0 DMA Legacy devices via AMAB AXI Coherent PCIe to 2<sup>nd</sup> SoC

DMA and peripherals

#### **Target to achieve**

Power <55.0W Number of frames in 20 ms > 28K Memory Bandwidth: 1 terabyte Three Explorations

1. AI and Tasks deployed in Software

2. AI tasks to custom AI processor

3. Power management to reduce power

### Scalable SoC Model

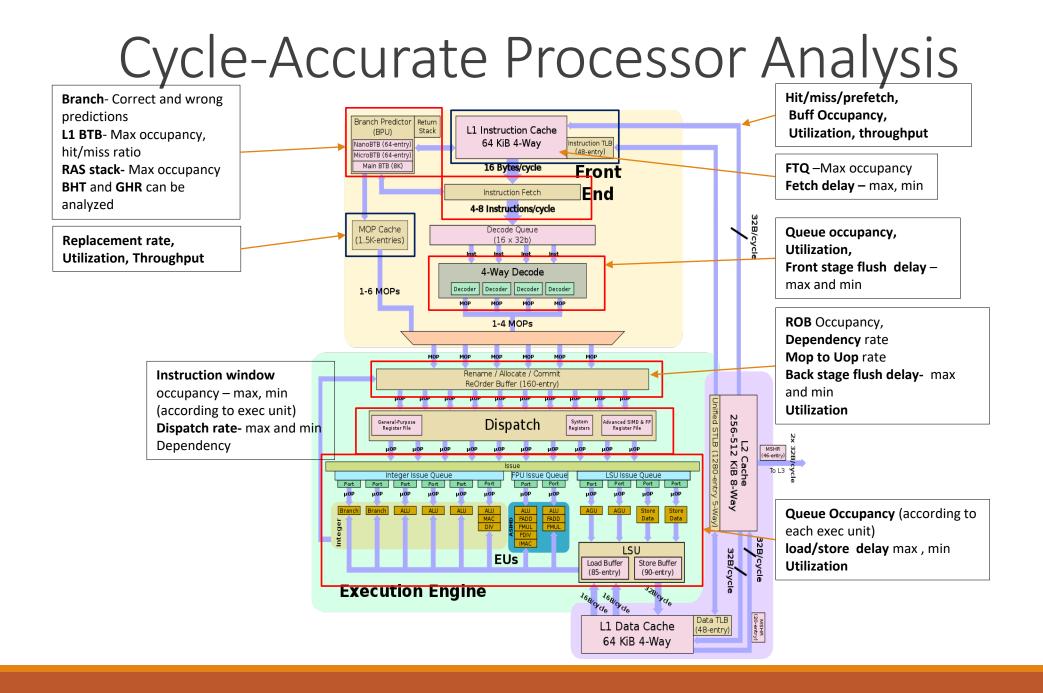

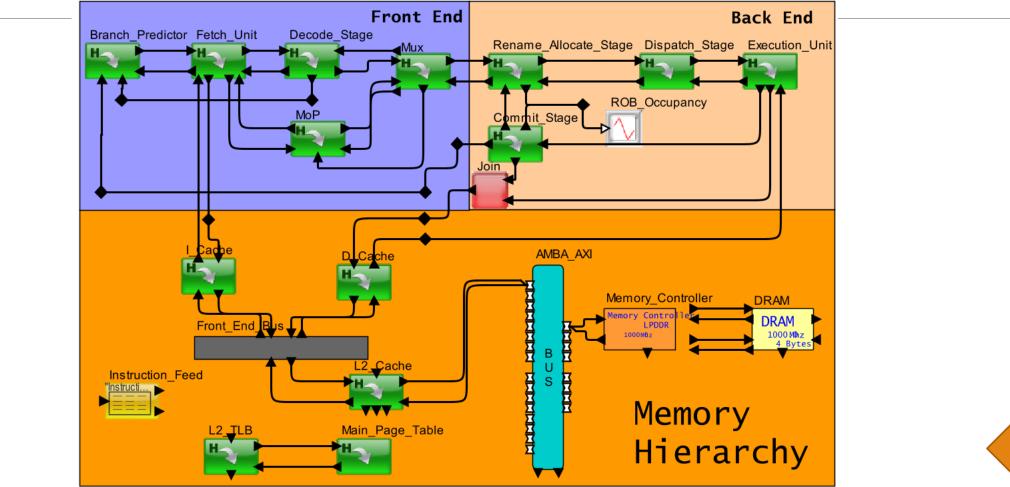

### MIRABILIS Using VisualSim Cycle-Accurate Library to Create an ARM A77

desi

Integrate Behavior, Timing, Power and Software

# Modeling, Simulation, Analysis and Recommendation using VisualSim

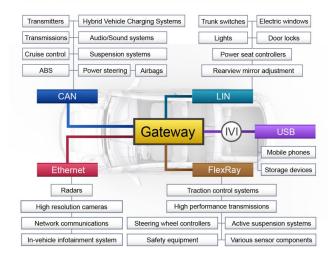

### Mission-to-Integration Analysis

### Mirabilis Design Users and Technology

Integrate corporate R&D, engineering and suppliers

# Modeling Abstraction Determines the Level of Accuracy

| Abstraction<br>Level | Type of<br>Library | Example                         | Accuracy | Limited by                                                     |  |

|----------------------|--------------------|---------------------------------|----------|----------------------------------------------------------------|--|

| Blocks               | Generic            | Resource-<br>based              | ~85%     | Available parameters                                           |  |

|                      | Specific           | AXI, DDR3,<br>Processor         | >97%     | Branch prediction<br>accuracy and minor<br>proprietary details |  |

| Scripts              | n/a                | User's<br>Hardware/<br>Software | 95%~     | None (can be exactly                                           |  |

| Coding               | n/a                | C/C++/RTL/S<br>ystemC           |          | to the hardware)                                               |  |

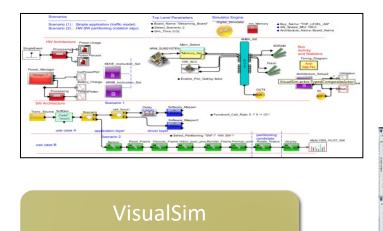

#### System Modeling 🔄 VisualSim Architect - file:/E:/VisualSim/VisualSim16\_64\_Jun. . .artitioning/SoC/Power\_Perf\_example.xml Ð $\times$ \_ File View Edit Graph Debug Interface Help ► ◆ 6. Variables/ 2.Documentation 1. Libraries Multimedia System Design Registers Scenarios Simulator **Top Level Parameters** 3. Parameters Document Digital\_Simulator Init Memory Board Name: "Streaming Board" Bus\_Name: "TOP\_LEVEL AXI" Scenario (1): Simple application (traffic model) Model Setup AXI Speed Mhz 166.0 Select Scenario: 2 Scenario (2): HW-SW partitioning (rotation algo) /Configure Traffic 0.0 Architecture Name: Board Nam Sim Time: 0.02 Results File IO AMBA AXI Behavior HW Architecture Power Usage Mappers Mem Select SDRAM Bus Resources SingleEvent ARM\_SUBSYSTEM Processing<sub>2</sub> Activity Power and Statistics lemory\_S Hardware Setup Power Percent Timing Diagram \_\_\_\_ Processor Generator HW ACC 9. Power Table Memory MOVE Instruction Set Arch State Plot Hardware Devices Interfaces and Buses InstPowerPlot Utilization Architecture Setup2 Full Library "Manager\_ UserLibrary 5. Hardware modeling Battery\_Charge ARM9\_Instruction Display\_Tex 7. Generate ≯Stati. OUT4 components Processing IN TimedPlotter Traces Arch SW Architecture Scenario 1 Software\_Mapper Delay call func() Trans\_Source SoftGen Scenario 4.Traffic/ Defining\_Flow->Mapping->S Internet Destaurier Industry Michigan 6. Use cases/ Behavior "mov Software Mapper2 Trace use case A application layer driver layer i 🔅 🙃 👘 partitioning Select\_Partitioning: "SW" /\* HW, SW \*/ cenario 2 candidate ANALYSIS\_PLOT\_SW Read\_Frame Decode\_Frame Video\_post\_proc Render\_Frame Format\_conv Rotate Frame display Sensor use case B linii 7. Report

## MIRABI IS

$\times$

### Simulate, Explore and Analyse

#### 1. Generate parameter variations to simulate on multi-core

|   | А                        | В            | С    |

|---|--------------------------|--------------|------|

| 1 | Parameter                | Range        | Step |

| 2 | Traffic_BW_Percentage    | {20.0;100.0} | 20.0 |

| 3 | Read_to_Write_Percentage | {25.0;100.0} | 25.0 |

#### 2. Setup the requirements and constraint file

|   | А               | В                | С          | D     | E |

|---|-----------------|------------------|------------|-------|---|

| 1 | Block_Name      | Stats_Name       | Constraint | Value |   |

| 2 | Smart_Resource  | Latency          | >          | 2     |   |

| 3 | Smart_Resource  | Buffer_Occupancy | >          | 25    |   |

| 4 | Smart_Resource2 | Utilization      | >=         | 0     |   |

| 5 |                 |                  |            |       |   |

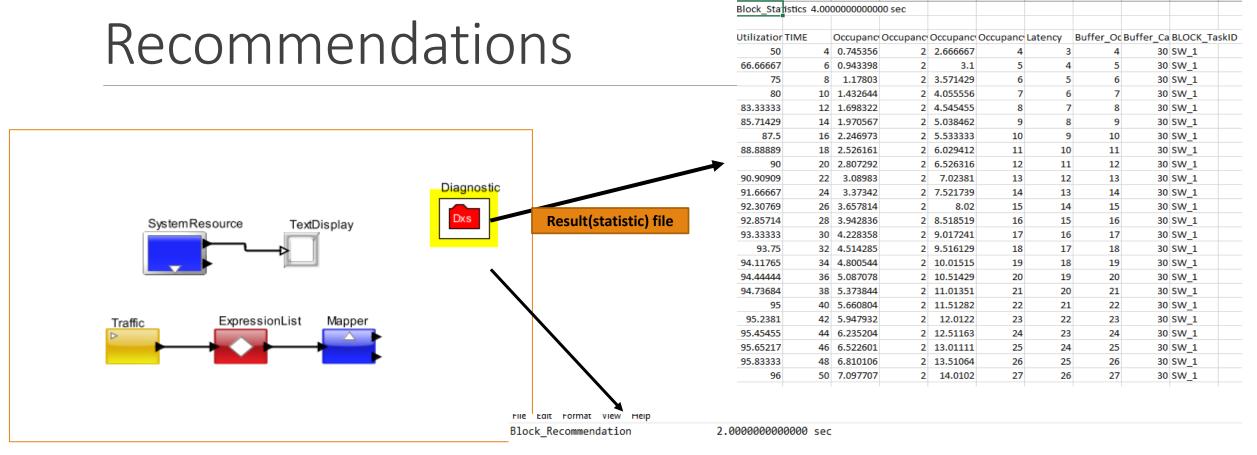

#### $\times$ NoC\_Mem\_TG\_Demo\_pp\_index.xml File Edit Activity Xml GnuPlot Comparator Batch Generator Model Plots End\_to\_End\_Latency\_1\_End\_to\_End\_Latency\_2.plt Select Parameters Vaffic\_BW\_Percentage=20.0,Mem\_Clock\_Speed\_Mhz=800.0,Read\_to\_Write\_Percentage=2 File Edit Activity Xml GnuPlot Comparator Batch Generator Traffic BW Percentage=40.0,Mem Clock Speed Mhz=800.0,Read to Write Percentage=40.0, ·10<sup>-5</sup> Traffic\_BW\_Percentage=60.0,Mem\_Clock\_Speed\_Mhz=800.0,Read\_to\_Write\_Percentage=2 End To End Latency Traffic\_BW\_Percentage=80.0,Mem\_Clock\_Speed\_Mhz=800.0,Read\_to\_Write\_Percentage=2 M1\_1 5 Traffic BW Percentage=100.0.Mem Clock Speed Mhz=800.0.Read to Write Percentage= M2\_1 • Traffic BW Percentage=20.0,Mem Clock Speed Mhz=800.0,Read to Write Percentage=4 4 M3\_1 • • Traffic BW Percentage=20.0,Mem Clock Speed Mhz=800.0 3 Select Plot M4\_1 • Input Buffer Occupancy\_Device M1\_2 2 Mem\_Stats M2 2 Power Plot M3 2 Input Buffer Occupancy East End To End Latency M4\_2 • 0.0 0.2 0.4 0.6 0.8 1.0 Input Buffer Occupancy Nort Input Buffer Occupancy Devi x10<sup>-4</sup> Input Buffer Occupancy\_Sout Input Buffer Occupancy\_Wes • View Plot View Selected Traces View All Traces

#### 3. Compare Results across Multiple Runs

Accelerate trade-offs and exploration by leveraging all available cores

Recommendation

file

SW block is not sending out any transaction. Check the resource to make sure the logic is correct at 2.000000000000 sec The loading on the SW is above the threshold at 4.000000000000 sec

- The loading on the SW is above the threshold at 6.000000000000 sec

- The loading on the SW is above the threshold at 0.00000000000 se

- The loading on the SW is above the threshold at 24.00000000000 sec

- SW is extremely busy and did not go below the threshold at 24.000000000000 sec

- The loading on the SW is above the threshold at 26.0000000000000 sec

- SW is extremely busy and did not go below the threshold at 26.000000000000 sec

## Software Performance Tuning

Process of accurately measuring the expected latency of a software code on a hardware or SoC platform using an architecture model

Used to plan the code sequencing and editing to maximize the processor efficiency

Eliminates the need for hardware boards for early testing and validation

### Methodology

| AI and Software Code                                                                                               | Modify the code to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Performance Reports                                                                              |  |  |

|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|--|

|                                                                                                                    | improve performance<br>And repeat loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Delay_95_StDev_196s = 4.39E-6<br>Latency_Value = 7.46E-6<br>Mean_95_Confidence = 3.61E-7         |  |  |

|                                                                                                                    | ie bild Saanh Viere Honding Langunge Sattings Nach Magen Window f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Mean_Value       = 4.01E-6         Min_Value       = 3.62E-7         StDev_Value       = 2.24E-6 |  |  |

| Machine A<br>Machine B<br>Machine<br>Senerates output<br>for ARM platform<br>Machine<br>ARM Machine<br>ARM<br>File | Image: Note: |                                                                                                  |  |  |

| Compile software<br>to target hardware                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Execute Software trace<br>on SoC Platform                                                        |  |  |

### System Verification

Validate product not just HW/SW

• Application relevant test vectors

Match architecture timing within **band range**

Verify software functionality

- Task sequencing @ DSP/uP

- Resource contention

Eliminate product failure by maximizing relevant verification

# Creating Early Visual Demonstrator and Executable Specification

#### System Architects

- Architecture Exploration, power and Performance analysis

- Dynamic use case and application profiling

- Fault and Reliability analysis

Architect

VisualSim Executable Specification

- Models can be viewed, modified and simulated within Web Page without a local install

- Experiment with different traffic and use cases.

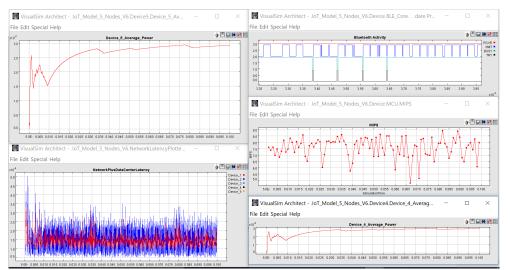

### Performance, Power and Functional Analysis

### Purpose of System Modeling

• Select the right platform

- ✓ Processor, FPGA or SoC

- Hardware-Software partitioning

- Trade-off power, performance and functionality

- Develop full system prototype

- ✓ Visibility into complete system operations

- View both implementation agnostic and effects

- When to perform system simulation

- Identify capacity limitation and bottlenecks

- Performance, Power or Functionality is non-deterministic

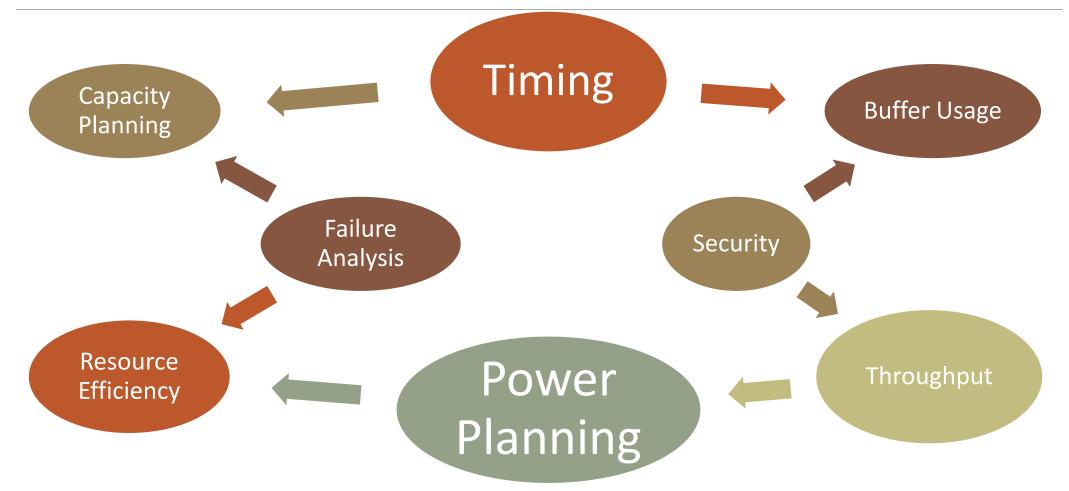

## Key Terms and Analysis

#### Architecture Exploration

• Is the process of evaluating the specification prior to development

#### System modeling

Construct virtual model to represent functionality, timing and power without the implementation code

#### Trade -off

- Select right configuration and parameters to meet requirements

- Evaluate task mapping, power vs timing, hardware vs software, distributed vs centralized etc.

#### Performance Analysis

• Buffer usage, utilization, throughput and latency

#### **Power Measurement**

Peak and average power, device and task energy consumption

#### **Functional Correctness**

• Arbitration, failure analysis, task scheduling and task graph

#### Making Better Quality Products

# Analysis to Identify Bottlenecks and Optimize System Specification

Over 500 pre-built reports and statistics

### Statistics and Plots for Accurate Analysis

Graphical and textual statistics

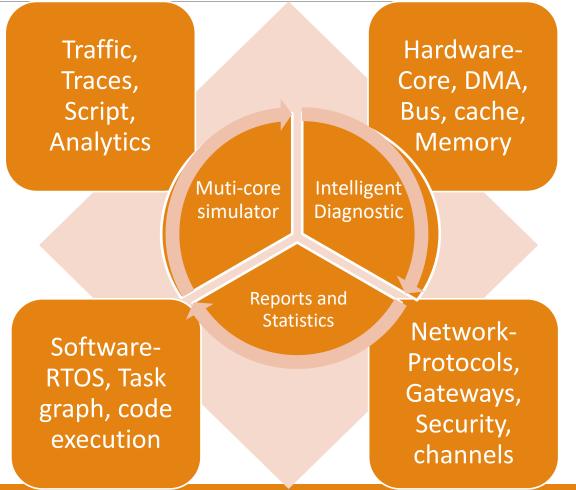

### VisualSim Solution Details

Rapid prototype of systems

- Use Library of modeling components of pipeline, SoC, software and system

- Make decision with Reports and metrics for performance, power and functionality

#### Select IP blocks and configure

- Partitioning algorithms onto cores/accelerators to meet requirements

- Intelligent Diagnostics provides recommendation on requirements-based feasibility based

#### Performance testing of AI/Application software

• Run traces of the C/C++/Python code on cycle-accurate SoC architecture model

Integration with design flow

- Generate dynamic documentation for use as specification

- Connect to FPGA boards for early system verification

Dynamic failure analysis for requirements validation and functional safety

### Example of Exploration

**IP** selection

- GDDR6 vs LPDDR5

- NoC vs custom fabric

#### Topology to meet latency and throughput

- Master and slave placement

- Distance between Routers

Hardware-software partitioning

Distribute tasks on cores, FPGA and multi-ASIC

#### Power-Timing trade-off

Instant power vs latency

#### Parameter selection

- Clock speeds

- Flit size, width

#### Functional

• Trade-off arbitration, scheduling, dispatcher

#### Protocol design

- Performance for algorithms and HW assignment

- Impact on network traffic and QoS

#### Software design

- Algorithm and control evaluation

- Test behavior for variable and state change

- Interaction between software components

#### **VISUALSIM TRAINING**