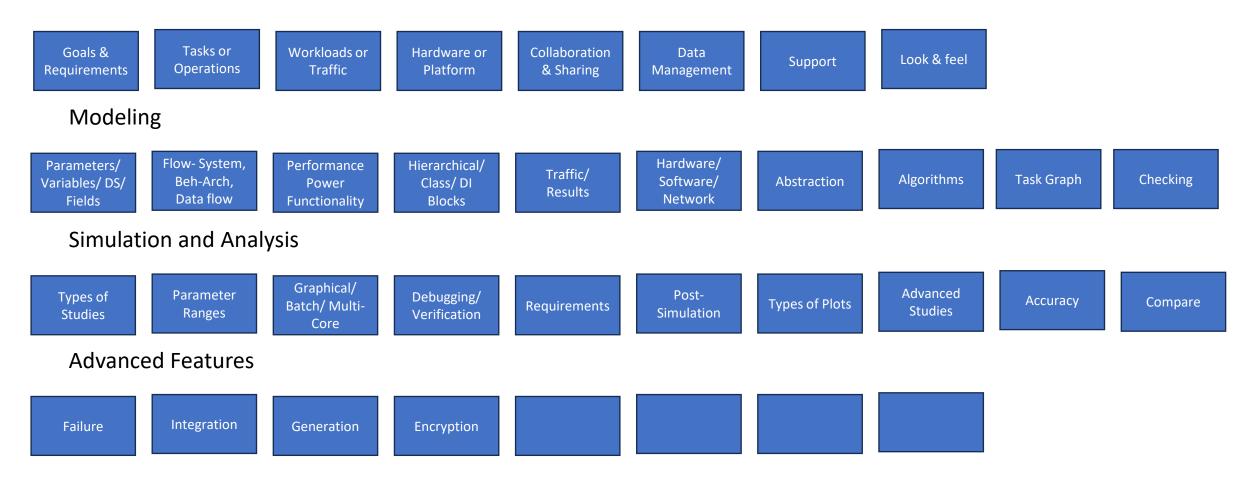

#### **VisualSim Training**

Training: Planning, Modeling, Simulation, Advanced Features MIRABILIS

#### Planning

## Agenda- Part 2: Modeling

- Basic Components for hardware modeling

- Performance, Power and Functionality

- Performance and power Metrics

- Library components and important parameters which affect performance

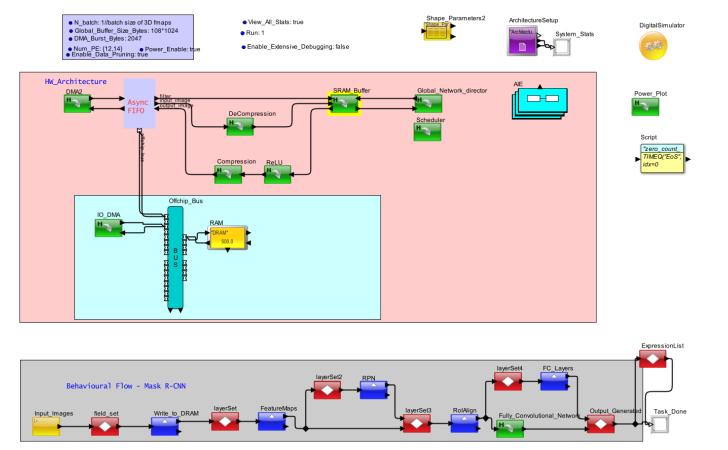

## Performance, Power and Functionality

- VisualSim provides an integrated solution for performance, power and functional modeling

- The details regarding Power modeling have been dealt in a separate presentation

- The functional modeling aspect is covered in modeling the task graphs section

- The user can also perform functional verification by observing the input, output values, checking for their correctness

- Custom algorithms or functional flows can also be define dusing the Script Block

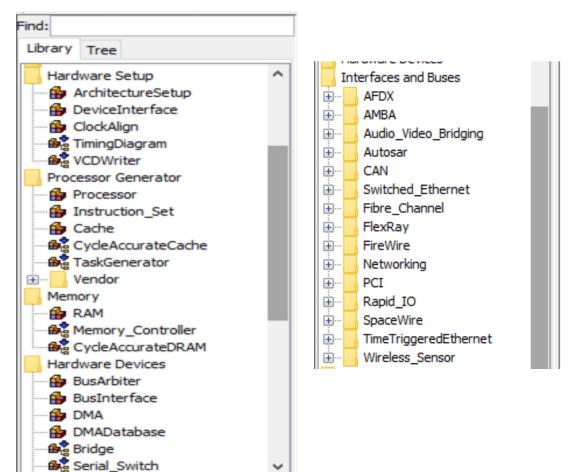

### **Basic Components for Hardware Modeling**

## Architecture Library Overview

- •Generate architecture with parameterized blocks

- Define hardware and software components

- Create proposed or derivative architectures in few minutes

- Rapidly define application flow diagram and behavior

- Optimize architecture and functionality mapping combination

### Hardware Modeling Library

$\sim$

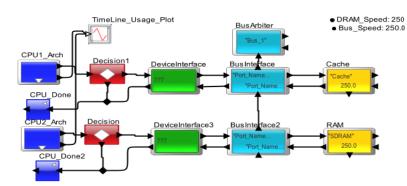

## Basic Components to define

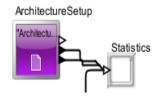

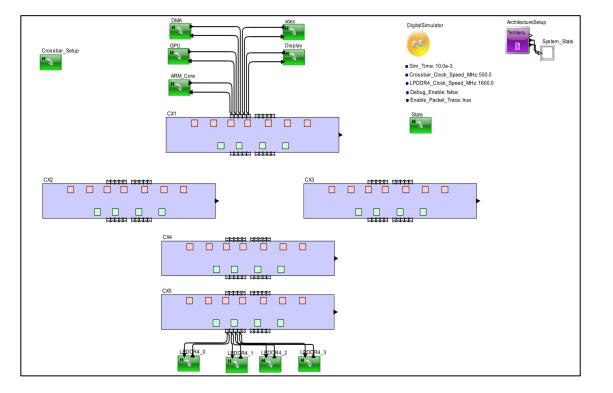

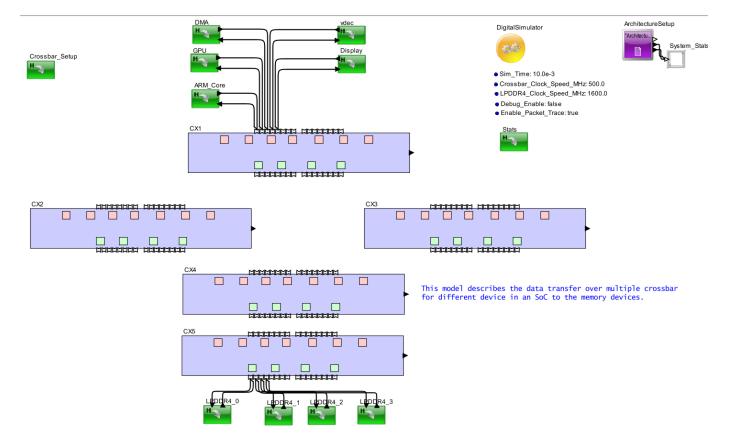

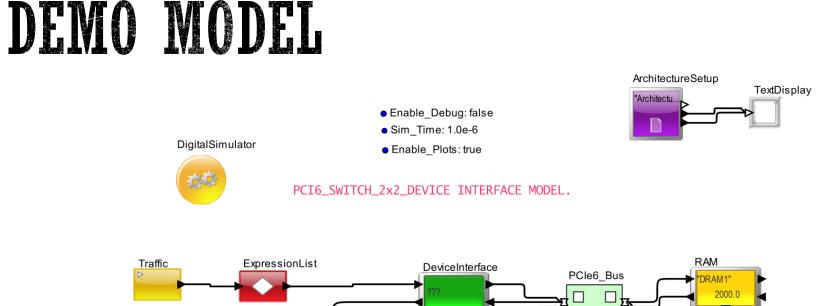

1. Hardware modeling requires Architecture\_Setup block - has the routing information of all hardware blocks in the model

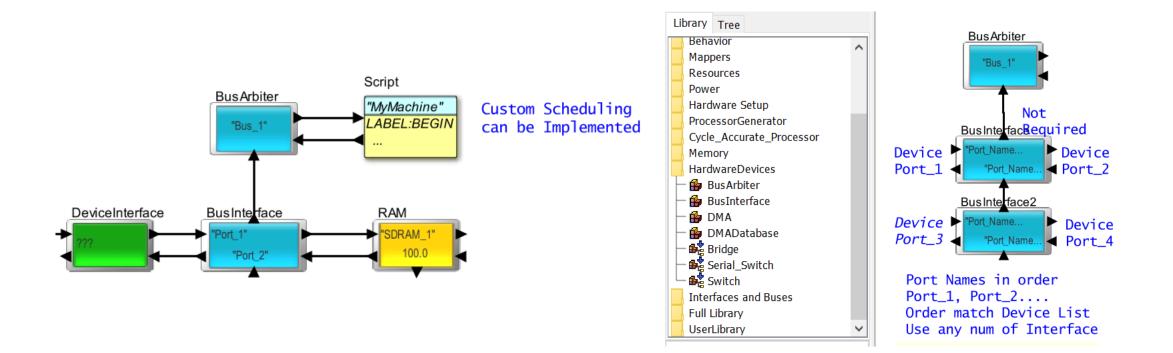

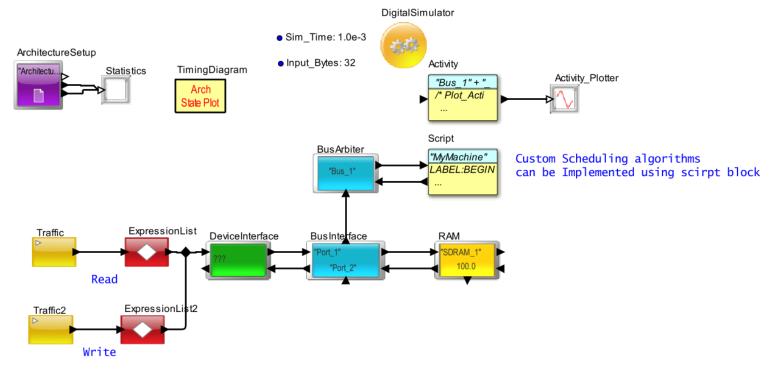

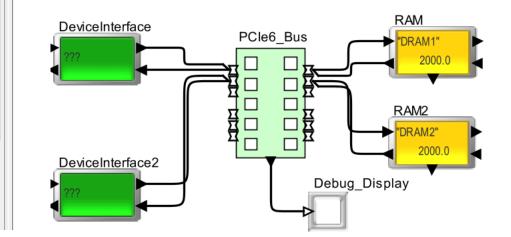

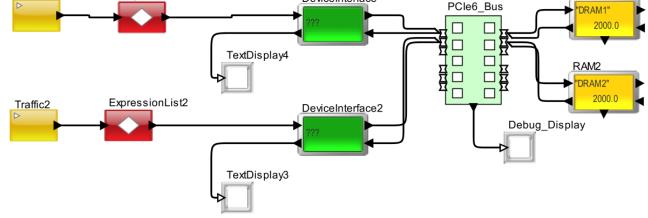

2. If using Traffic or other custom block to connect to a Bus, use the Device\_Interface block in front of the Bus port.

- Also true for AXI, PCIe and NoC

- Not required for Standard Blocks Like Processor

- 3. Processor block requires Instruction\_Set

ArchitectureSetup Block gives out statistics for all the hardware blocks in the model

#### Use of Device Interface

Processor Blocks with InstructionSet

Step2

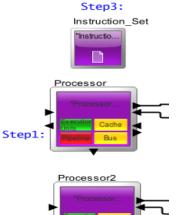

# Architecture Setup

#### All Bus and Hardware block must associate with Architecture Setup

This Block Handles

➢ Routing

➢ Plotting

Statistics

> Debugging for all the Hardware components

There can be multiple architecture setup blocks

2. Each block must have unique name

#### Note: this Block can be used as it is after updating the Architecture\_Name field

### Custom Routing Table Construction - in Architecture Setup

#### Format Sample:

| Source_Node | Destination_Node | Hop Sourc  | e_Port   |

|-------------|------------------|------------|----------|

| Source      | Destination      | Next Block | Out Port |

| Processor   | DRAM             | Port_1     | bus_out  |

#### Add entries using RegEX

addToRoutingTable (Architecture\_Name, Source\_Name, Destination\_Name, Hop\_Name, Source\_Port\_Name)

### Delete entries using RegEX

removeFromRoutingTable (Architecture\_Name, Source\_Name, Destination\_Name, Hop\_Name, Source\_Port\_Name)

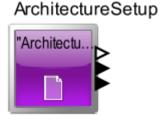

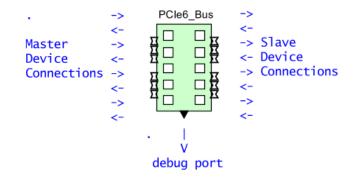

## DeviceInterface Block

- Can be used to define the Source Name, data size, command type and destination for a Master

- Can be used to define the Device name on the Slave side

- Add the Master or Slave block to the Linear Bus, Bridge and AHB Buses automatically

- ✓ Generate Hello Messages

- ✓ Eliminates the need for a RegEx functions or manually generate Hello message

- Map fields of other data structure formats to the corresponding fields of the Processor\_DS

- Used to connect only in the presence of the Linear Bus, AHB and bridge blocks.

- Not useful with a single AXI or a single PCIe

| Block_Documentation: | D Enter User Documentation Here |

|----------------------|---------------------------------|

| Architecture_Name:   | "Architecture_1"                |

| A_Source:            | "CPU2"                          |

| A_Destination:       | "Cache"                         |

| A_Command:           | "A_Command"                     |

| A_Instruction:       | "Fld_Name_or_String_or_None"    |

| A_Bytes:             | "A_Bytes"                       |

| A_Priority:          | "Fld_Name_or_Integer"           |

| A_Address:           | "Fld_Name_or_Integer"           |

|                      |                                 |

| Commit               | Add Remove                      |

Set field values here or keep default to use existing field values

### Stochastic Components in the Library

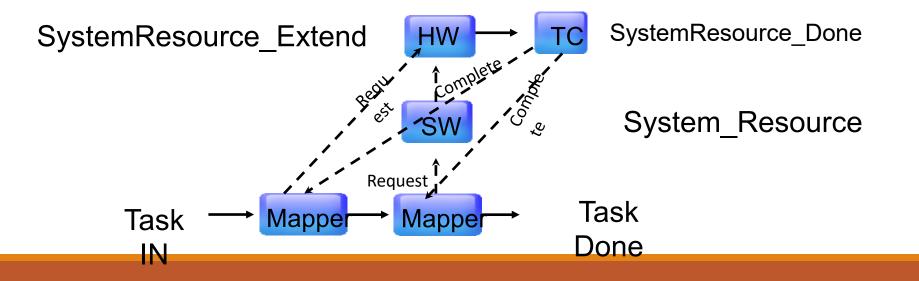

## Concept of System Resource

#### Concept

- Split operation into two parts

- Behavior or mapper

- Resource (similar to Server)

#### Blocks

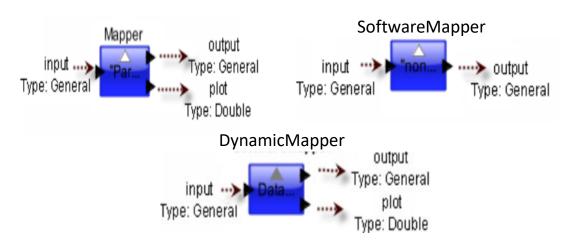

- Behavior: Mapper, SoftwareMapper, DynamicMapper

- Architecture: SystemResource\_Extend, SystemResource

- Notify: SystemResource\_Done

#### Multiple concurrent requests

- Send from Mapper (Behavior) to the SystemResource with the delay information

- Can be static or dynamic reference

- Scheduler: First Come-First Serve, Round-Robin, Preemption, Non-Locking

#### SystemResource\_Done block

Release appropriate SystemResource\_Extend block by signaling the completion of an external task

#### SystemResource task\_output Schedu... Type: General Type: Double SystemResource\_Extend Type: General Type: Double SystemResource\_Done Type: General Type: Double

#### Architecture

#### **Behavior**

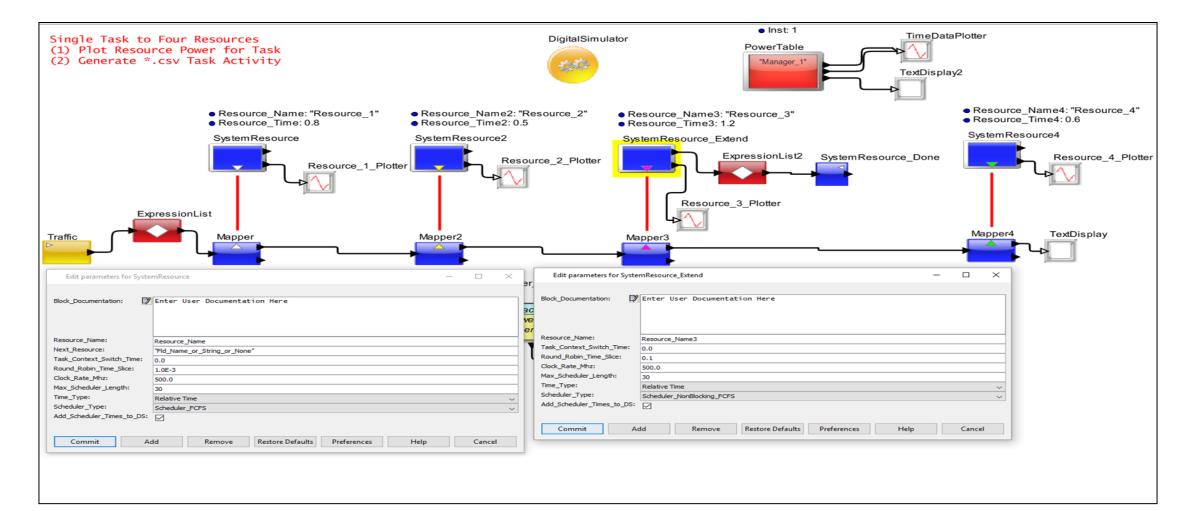

## Mapper to System Resource

- Mapper blocks define the connectivity between the behavior flow and the architecture flow, and within the architecture flow using a named connection

- The block takes the incoming Data Structure and send it to the Scheduler virtually

- This block can send a request to either the SystemResource or SystemResource\_Extend.

#### SystemResource task\_output "Schedu...">Type: General task\_plot Type: Double

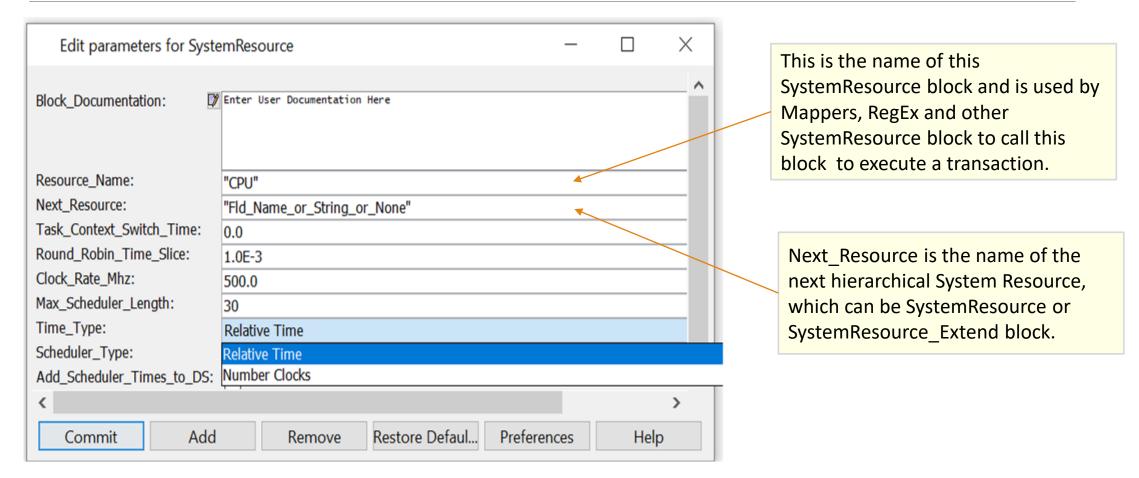

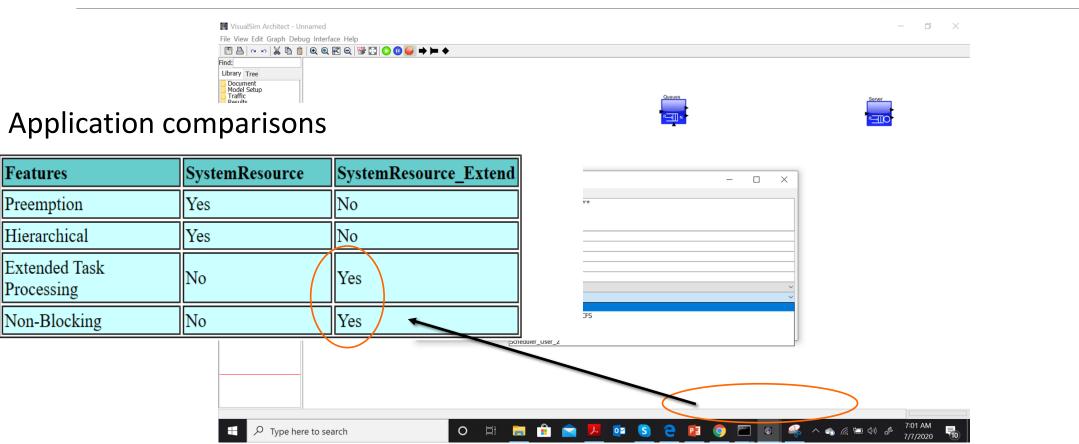

## System Resource (Cont.)

| Edit parameters for SystemResource |                               |  | ×    |         | Time the scheduler will devote to each task for Round Robin |                |                       |  |

|------------------------------------|-------------------------------|--|------|---------|-------------------------------------------------------------|----------------|-----------------------|--|

| Block_Documentation:               | Enter User Documentation Here |  |      | Ар      | plicatio                                                    | on comp        | arisons               |  |

| Resource_Name:                     | "CPU"                         |  |      | Featur  | es                                                          | SystemResource | SystemResource_Extend |  |

| Next_Resource:                     | "Fld_Name_or_String_or_None"  |  |      | Preemp  | tion 🖌                                                      | Yes            | No                    |  |

| Task_Context_Switch_Time:          | 0.0                           |  |      | Hierarc |                                                             | Yes            | No                    |  |

| Round_Robin_Time_Slice:            | 1.0E-3                        |  |      |         | ed Task                                                     |                |                       |  |

| Clock_Rate_Mhz:                    | 500.0                         |  |      | Process |                                                             | No             | Yes                   |  |

| Max_Scheduler_Length:              | 30                            |  |      | Non-Bl  | ocking                                                      | No             | Yes                   |  |

| Time_Type:                         | Relative Time                 |  |      |         | 0                                                           |                |                       |  |

| Scheduler_Type:                    | Scheduler_FCFS                |  | <br> | ٦       |                                                             |                |                       |  |

| Add_Scheduler_Times_to_DS:         | Scheduler_FCFS                |  |      |         | Cot Cobo                                                    | dular tupa f   | rom the renge         |  |

| (                                  | FCFS + Preempt                |  |      | Ļ       |                                                             |                | rom the range         |  |

| Commit                             | Scheduler_RR                  |  |      |         | of sched                                                    | aulers         |                       |  |

| Commit Add                         | Scheduler_User_1              |  |      |         |                                                             |                |                       |  |

|                                    | Scheduler_User_2              |  | <br> |         |                                                             |                |                       |  |

- Double click to configure

System Resource Extended

## What is Mapper?

#### Connect behavior flow with architecture resources

- Takes incoming Data Structure and sends to

- SystemResource

- SystemResource\_Extend blocks

Mapper

- Placed in the behavior flow where timed resources required

- Consumes zero time, no queue, no arbitration

| Edit parameters for Mapper3                                                                                                                                      | _         |     | × | Edit parameters for SystemResource —                                                                                                                                                                              | $\times$ |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Block_Documentatio 🗊 Enter User Documentation Here                                                                                                               |           | _   |   | Block_Documentation: 🎲 Enter User Documentation Here                                                                                                                                                              | ^        |

| Target_Resource:     CPU       Task_Number.     1       Task_Priority:     Task Priority Eld Int Dbl Expr                                                        |           |     |   | Resource_Name;       "CPU"         Next_Resource:       "Fld_Name_or_String_or_None"         Task_Context_Switch_Time:       0.0         Round_Robin_Time_Slice:       1.0E-3         Clock_Rate_Mhz:       500.0 | -        |

| Task_Priority:     Task_Priority_Fld_Int_Dbl_Expr       Task_Time:     input.time       Task_Plot_ID:     1       Commit     Add     Remove     Restore Defaults | Preferenc | ces |   | Max_Scheduler_Length:     30       Time_Type:     Relative Time       Scheduler_Type:     Scheduler_FCFS       Add_Scheduler_Times_to_D                                                                           | ~        |

input ..... Mapper output input ..... Type: General Type: General plot Type: Double

System Resource

### Software Mapper Hardware or Software Task issuer

- Sends tasks to SystemResource or SystemResource\_Extend based on Target\_Resource

- Block can either Queue incoming Data Structure or send to SystemResource immediately

|                                    |   | Edit parameters for                                                                               | SoftwareMapper                                               |               |                  | -           | - 🗆  | $\times$ |               |                                  |  |

|------------------------------------|---|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------|---------------|------------------|-------------|------|----------|---------------|----------------------------------|--|

| Attributes to issue<br>the task to |   | Edit parameters for<br>Block_Documentatio [<br>Target_Resource:<br>Task_Number:<br>Task_Priority: |                                                              | Documentation | Here             |             |      | ×        |               |                                  |  |

| System Resource                    |   | Task_Mean_Time:<br>Task_Spread_Time:<br>Random_Seed:<br>Task_Distribution:                        | Scan_Proc_Time<br>Task_Spread_Flo<br>123457L<br>Fixed (Mean) |               |                  |             |      |          | <br>preemptin | Il other tasks<br>g this Task at |  |

|                                    | 5 | Task_Type:<br>Task_Mutual_Exclusion:                                                              | Queue Task Nov                                               | 1             |                  |             |      | ×<br>  × | SystemRes     | ource                            |  |

|                                    |   | Commit                                                                                            | Add                                                          | Remove        | Restore Defaults | Preferences | Help |          |               |                                  |  |

File View Edit Graph Debug Interface Help  $\blacksquare$ 📇 🗠 က 👗 🗨 🔍 🛃 🗨 🔛 💽 ĥ Find: Library Tree Test Model - Scheduler Digital Document Model Setup PowerTable2 Traffic TASK: "SW" 00 TimeDataPlotter Results "Manager\_1" File IO Behavior Mappers Task Creation. Resources TextDisplay Power SystemResource Traffic Mapper Hardware Setup The PowerTable is updated with ProcessorGenerator xTimeyDataPlot the power consumed by the Cycle\_Accurate\_Processor SystemResource blocks. Memory Note that the Reg-Ex expression Traffic2 Mapper2 HardwareDevices regarding power\_manager is used in the  $\wedge$ Interfaces and Buses ExpressionList block. Full Library UserLibrary Traffic3 Mapper3  $\bigtriangleup$ PowerManager 3 tasks competing for the Current Test Model - Scheduler Digital Traffic4 ExpressionList same resource Cumulative execution finished. 12:14 PM ∧ © "□ *(i*, ⊄») *₫* S C:N\_ ٢ Ω Type here to search Ξi P 16 2/16/2024

\$VS/doc/Training Material/Tutorial/General/System Resources/Scheduler Sw 2.xml

SusualSim Architect - file:/C:/VisualSim/VisualSim2340\_64/V. . . I/System\_Resources/Scheduler\_SW\_02.xml

\_

D

$\times$

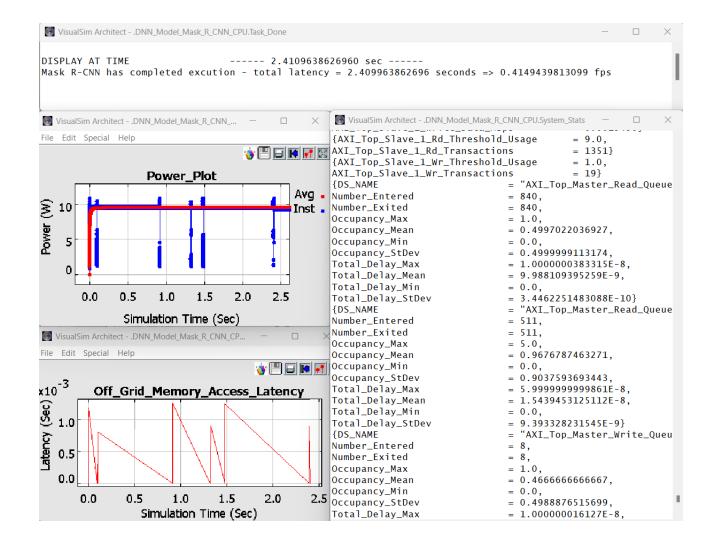

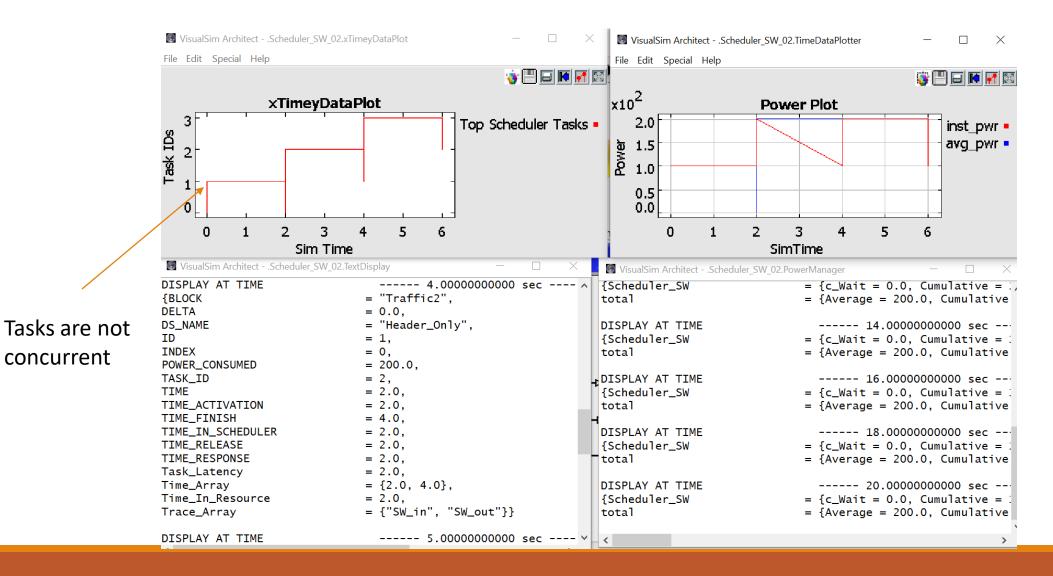

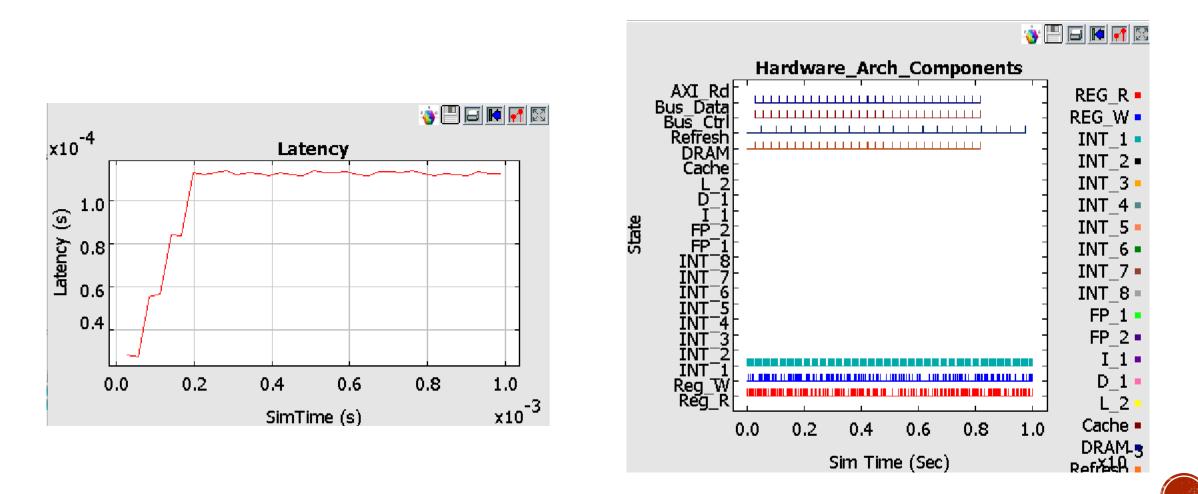

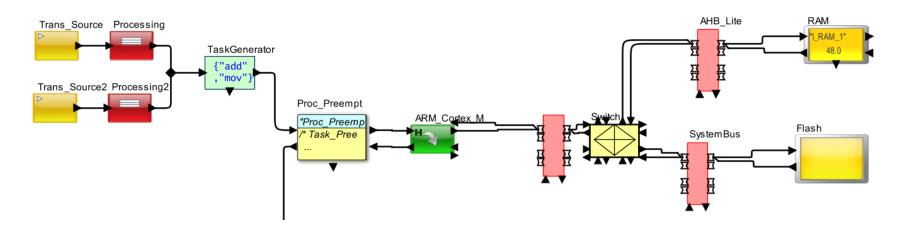

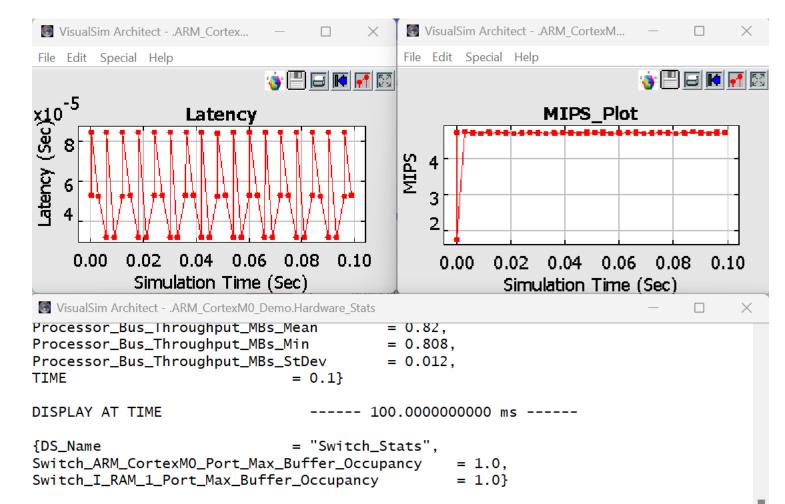

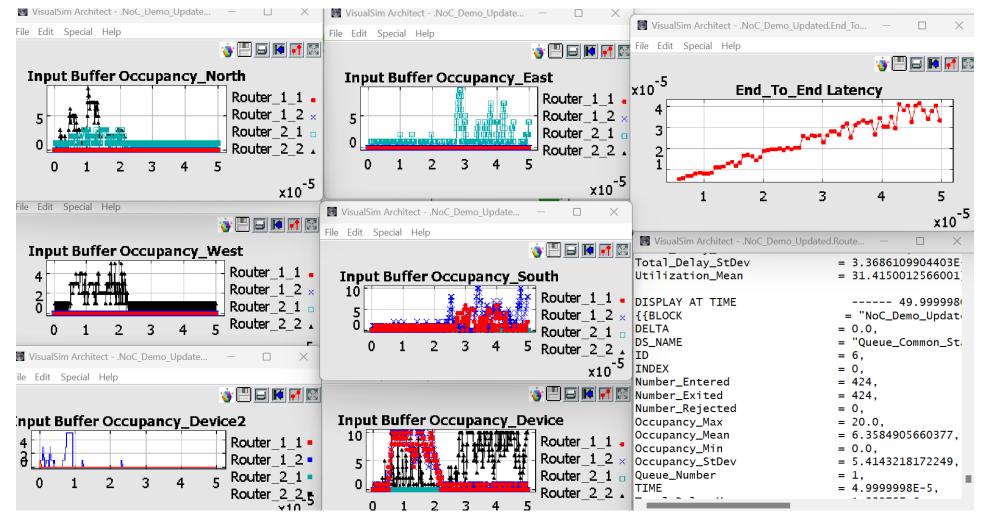

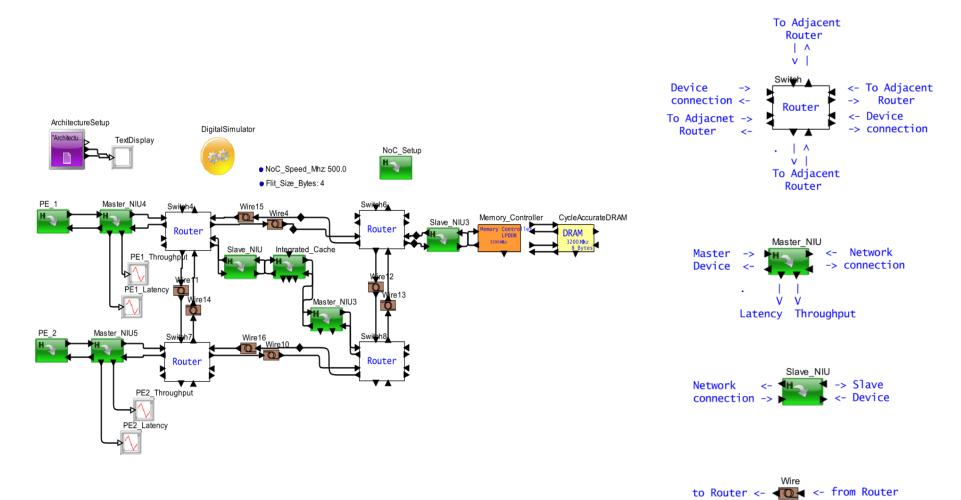

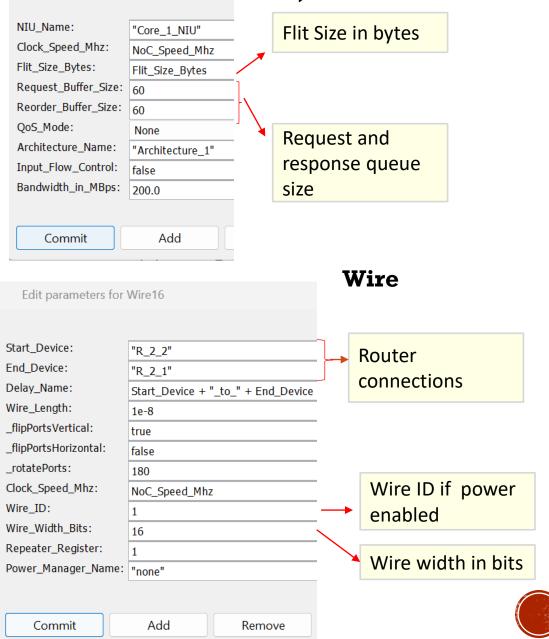

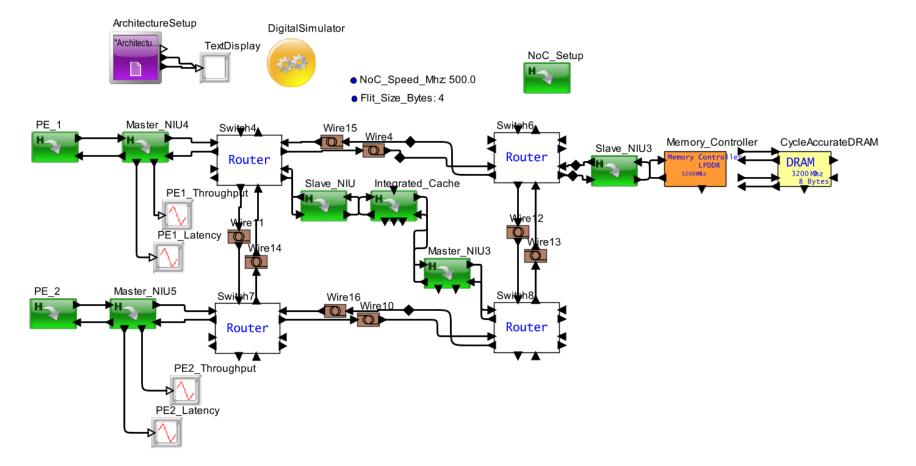

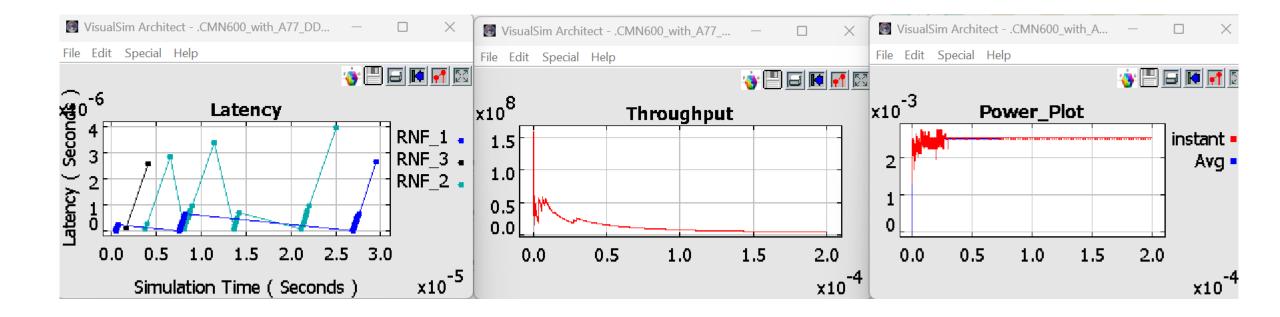

## Plots and Stats for Example Model 1

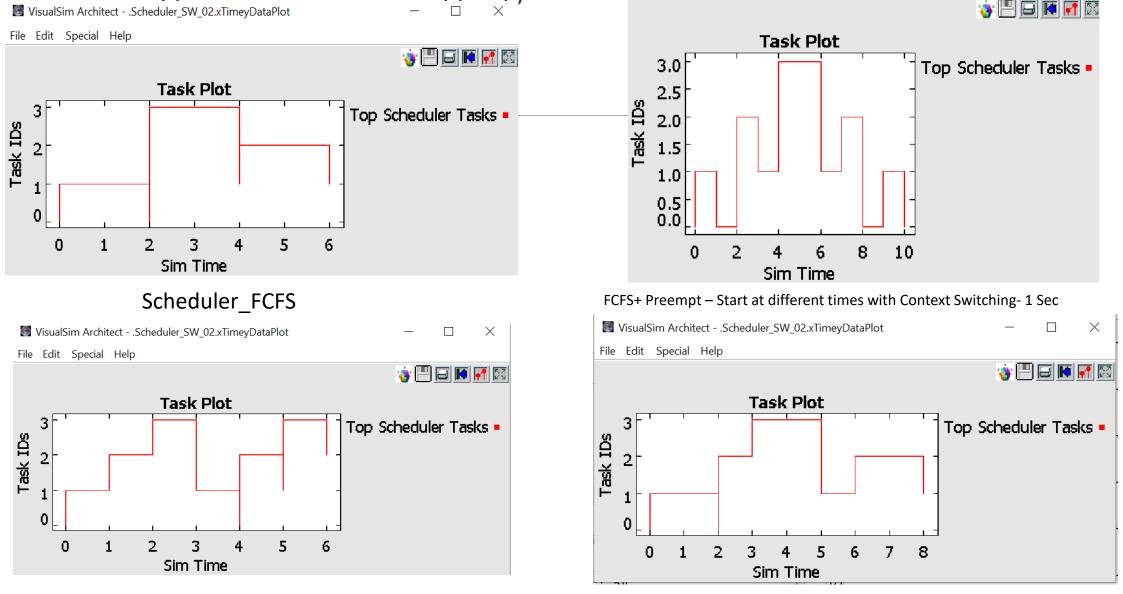

## Different Types of Scheduling Algorithms in SystemResource

Scheduler\_RR

#### Scheduler\_FCFS+Preempt

## Example Model – System Resource Extend

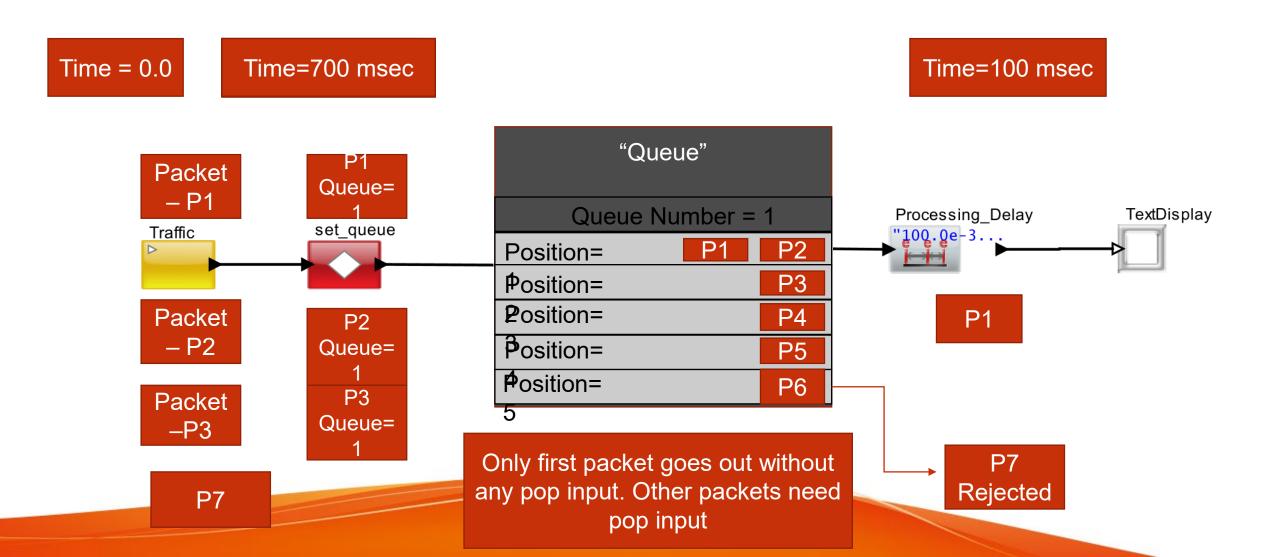

## Queue

|                         |                               |                              | Queues                                                       |

|-------------------------|-------------------------------|------------------------------|--------------------------------------------------------------|

| Edit parameters for Q   | lueues                        | _                            | input, output                                                |

| Block_Documentation:    | Enter User Documentation Here |                              | P reject_output                                              |

| Block_Name:             | "Queue"                       |                              |                                                              |

| Queue_Number_Field:     | input.queue                   | Provides the priority number | Queue-N Transaction are                                      |

| Priority_Field:         | input.priority                | for reordering the queue.    | pushed out according to the                                  |

| Max_Queue_Length:       | 30                            | for reordering the queue.    | arbitration scheme                                           |

| Number_of_Queues:       | 1                             |                              | T4 T3 Queue2                                                 |

| Initial_Queue_State:    | First_Token_Flow_Through      |                              |                                                              |

| Queue_Reject_Mechanism: | Incoming_Token_Rejected       | Set how the packets should   | T2 T1 Queue1                                                 |

| Queue_Type:             | FIFO                          |                              | Transaction are sent Transaction are                         |

|                         |                               | flow                         | to respective Queue arranged as per priority<br>According to |

| Commit A                | dd Remove Restore             | Defaul Preferences Help      | Queue_No                                                     |

|                         |                               |                              | Queue N with Priority                                        |

Mirabilis Design Inc.

23 Return

## Queue – First Token Flow Through

## Queue – First token Enqueue

pop\_input is required to send all the packets including the first one

| Number_of_Queues:       | Number_Of_Queues        |

|-------------------------|-------------------------|

| nitial_Queue_State:     | First_Token_Enqueue     |

| Queue_Reject_Mechanism: | Incoming_Token_Rejected |

| Queue_Type:             | FIFO                    |

|                         |                         |

## Multiple number of Queues

| Edit parameters for Qu  | ieues — 🗆 X                                         |        | Internally, it look like this |

|-------------------------|-----------------------------------------------------|--------|-------------------------------|

| Block_Documentation: 🗊  | Enter User Documentation Here                       |        | "Queue"                       |

| Block_Name:             |                                                     |        | Q Num=1 Q Num=2 Q Num=3       |

| Queue_Number_Field:     | "Ingress_Queue"                                     | Pos=   | P1 P3 P5                      |

|                         | input.Queue_Num                                     |        |                               |

| Priority_Field:         | Int_Dbl_Expr_Mem_Fld                                | ∲os= 2 | P2                            |

| Max_Queue_Length:       | 5                                                   | 103-2  |                               |

| Number_of_Queues:       | 3                                                   | Pos= 3 | P4                            |

| Initial_Queue_State:    | First_Token_Enqueue ~                               |        |                               |

| Queue_Reject_Mechanism: | Incoming_Token_Rejected ~                           | Pos= 4 |                               |

| Queue_Type:             | FIFO                                                | Pos= 5 |                               |

|                         |                                                     | F05- 5 |                               |

| Commit                  | Add Remove Restore Defaults Preferences Help Cancel |        |                               |

pop\_input value can be 1, 2 or 3

### **Queue Operation - Summary**

- Data Structures are queued based on priority from high to low number

- Data Structures in the queue are arranged based on FIFO or LIFO setting

- Number\_of\_Queues defines the number of parallel queues contained by a single Queue block

- Queue Number Field selects the queue to place

- To pop a packet

- From the head of a queue, Queue\_Number must be sent to pop\_input port.

- When Maximum\_Queue\_Length is reached, packets are Rejected based on Rejection\_Mechanism and sent to Reject\_output

- Based on initial Queue State parameter,

- Enqueue: First Transaction can be enqueued and wait for the pop

- First\_Packet\_Flow\_Through: First transaction send without pop. After first packet, head of queue sent if prior was acknowledged with pop

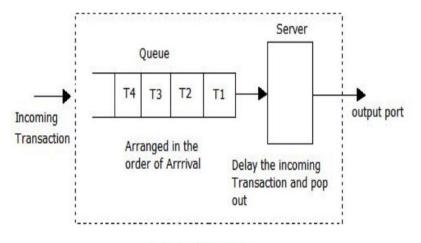

## Server

- Define multiple {queues + time delay}

- Active Resource

- DataStructures queued in FIFO or LIFO order

- Processing time is known in advance

- Provided along with the transaction to this block.

- SLOT

- Special operation mechanism

- Models any slot-based architecture such as multiple virtual RTOS, TDMA etc.

Basic Timed Queue

## Server

| Edit parameters for  | Server                        |                               | - |      | × |

|----------------------|-------------------------------|-------------------------------|---|------|---|

| Block_Documentation: | Enter User Documentation Here |                               |   |      |   |

|                      |                               | Server has a special          |   |      |   |

| Block_Name:          | "server"                      | parameter called "Time        |   |      |   |

| Queue_Number_Field:  | input.queue                   | field" to delay head of queue |   |      |   |

| Priority_Field:      | input.priority                | before sending out            |   |      |   |

| Time_Field:          | input.time                    | <u> </u>                      |   |      |   |

| Max_Queue_Length:    | 30                            |                               |   |      |   |

| Number_of_Queues:    | 1                             |                               |   |      |   |

| Queue_Type:          | FIFO                          |                               |   |      | ~ |

|                      |                               |                               |   |      |   |

| Commit               | Add Remove Restor             | re Defaul Preferences Help    |   | Cano | e |

Number\_of\_Queues can be multiple in the Server as well

29Return

## Server - Summary

- *Queue\_Number\_Field* selects the queue

- Queue is reordered based on *Priority field*

- Queue data in FIFO or LIFO based on *Queue\_Type*

- Delayed by *Time\_Field* value at head of queue and sent out

- Packet is sent to *reject\_output* when Max\_Queue\_Length reached

| Edit parameters for S                                                                                          | erver                                                     | _ |        | × |

|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|---|--------|---|

| Block_Documentation: 🚺                                                                                         | Enter User Documentation Here                             |   |        |   |

| Block_Name:<br>Queue_Number_Field:<br>Priority_Field:<br>Time_Field:<br>Max_Queue_Length:<br>Number_of_Queues: | "Server"<br>input.Queue_Num<br>1<br>input.Delay<br>30     |   |        |   |

| Queue_Type:                                                                                                    | 5<br>FIFO<br>Add Remove Restore Defaults Preferences Help |   | Cancel | ~ |

## **Performance and Power Metrics**

#### Common Statistics

- ✓ End-to-end latency and Task Delay

- ✓ Throughput (MIPS or MB/s), Utilization (%)

- ✓ Minimum, maximum, mean and standard deviation statistics

- ✓ Power Instantaneous, Average and Cumulative

- ✓ Battery Current Capacity(Watt Hr), Battery Life Remaining (%)

#### Processor

- ✓ Individual statistics for Caches, Execution Units and Pipeline Stages

- ✓ Flush Time, Stall (%), Thread swaps and Context switching

- ✓ Listener for Real-Time pipeline activity

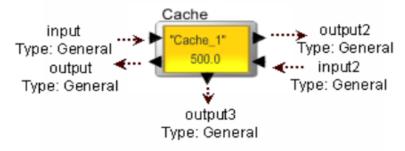

Cache

#### ✓ Hit-miss Ratio

✓ Requests, utilization, evictions, prefetches and latency and throughput

### Hardware Statistics

| Name                                          | Value       | Name                                          | Value         | Name                                                                | Value            |

|-----------------------------------------------|-------------|-----------------------------------------------|---------------|---------------------------------------------------------------------|------------------|

| Bus_1_Utilization_Pct_Max                     | 10.1,       | Bus_1_Delay_Max                               | 3.600004E-8,  | Processor_1_D_1_Hit_Ratio_Max                                       | 100.0,           |

| Cache_1_Utilization_Pct_StDev                 |             | Bus_1_IOs_per_sec_StDev                       | 634428.24721, | Processor_1_D_1_KB_per_Thread_StDev                                 | 0.0,             |

|                                               |             |                                               |               | Processor_1_I_1_Hit_Ratio_Max                                       | 100.0,           |

| Processor_1_D_1_Utilization_Pct_Max           | 1.45,       | Bus_1_Input_Buffer_Occupancy_in_Words_Max     | 32.0,         | Processor_1_I_1_KB_per_Thread_StDev                                 | 0.0,             |

| Processor_1_INT_1_Utilization_Pct_StDev       | 0.10969973, | Bus_1_Preempt_Buffer_Occupancy_in_Words_StDev | 0.0,          | Processor_1_L_2_Hit_Ratio_Max                                       | 100.0,           |

| Processor_1_INT_2_Utilization_Pct_Max         | 24.55,      | Bus_1_Throughput_MBs_Max                      | 176.0,        | Processor_1_L_2_KB_per_Thread_StDev                                 | 0.0,             |

| Processor_1_I_1_Utilization_Pct_StDev         | 0.01500007, | Cache_1_Delay_Time_StDev                      | 1.499871E-8,  | Processor_1_Stall_Time_Pct_Max                                      | 1.35,            |

| Processor_1_L_2_Utilization_Pct_Max           | 3.1,        | Cache_1_Hit_Ratio_Max                         | 100.0,        | Processor_1_Task_Delay_StDev                                        | 2.9502E-7,       |

| Processor_1_PROC_Utilization_Pct_StDev        | 0.03489914, | Cache_1_Memory_Used_By_Processor_1_MB_StDev   | 8.455181E-5,  | SDRAM_1_Delay_Time_Max                                              | 1.5E-7,          |

| Processor_1_Pipeline_Utilization_Pct_Max      | 50.2,       | Cache_1_Memory_Used_By_SDRAM_1_MB_Max         | 2.56E-4,      | SDRAM_1_Memory_Used_By_Processor_1_MB_StDev                         | 0.0,             |

| Processor_1_Register_Rd_Utilization_Pct_StDev | 0.19330594, | Cache_1_Memory_Used_By_Total_MB_StDev         | 8.455151E-5,  | SDRAM_1_Memory_Used_By_Total_MB_Max<br>SDRAM_1_Throughput_MBs_StDev | 2.56E-4,<br>0.0, |

| Processor_1_Register_Wr_Utilization_Pct_Max   |             | Cache_1_Throughput_MBs_Max                    | 116.0,        | DMA_IO_per_sec_Max                                                  | 7.45E6,          |

|                                               | 1.91E-07    | Processor_1_Context_Switch_Time_Pct_StDev     | 0.0,          | DMA_Throughput_MBs_StDev                                            | 3.463999999,     |

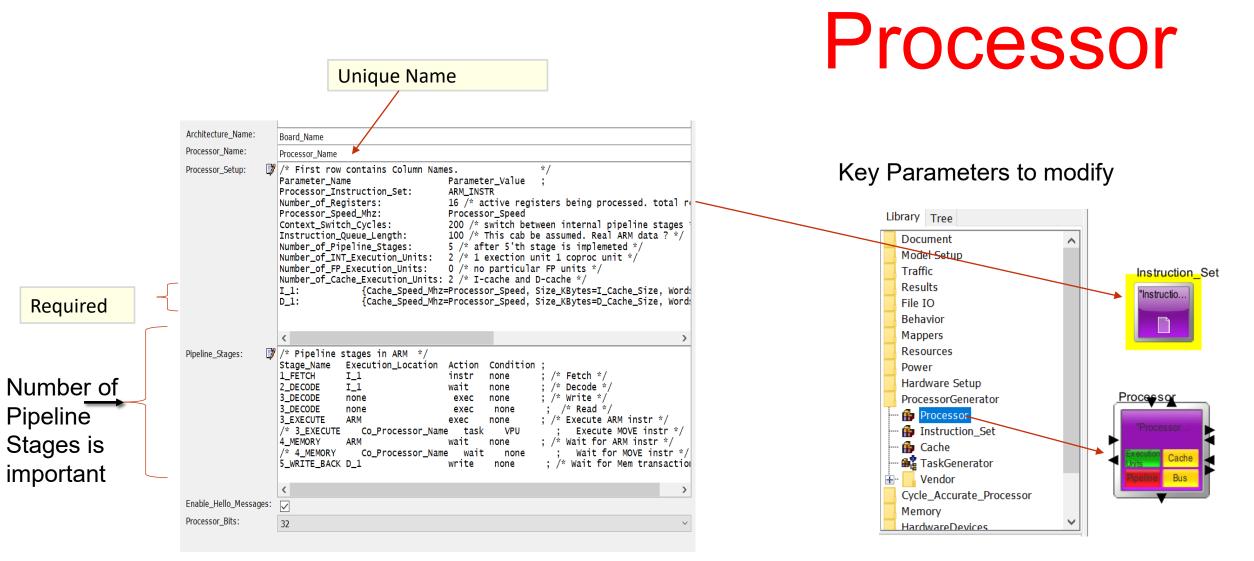

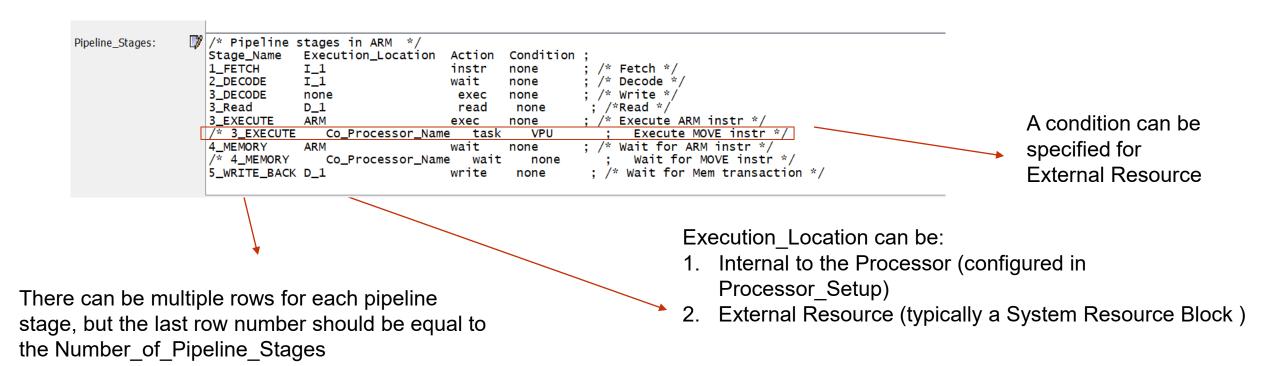

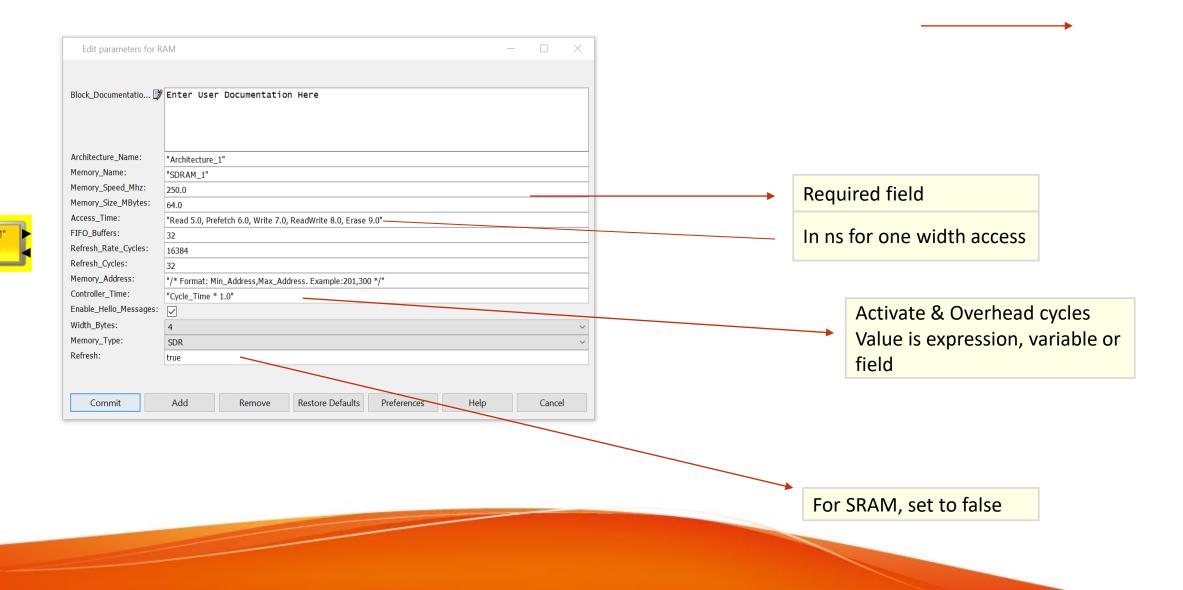

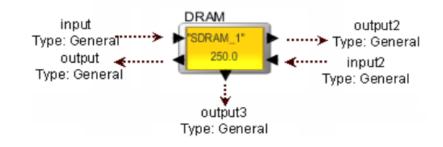

### Analyzing Performance in VisualSim – Important Parameters in Library Components

### Hybrid Processor

Outstanding\_Req\_Count is used for External Cache

### **Processor – Internal Cache Configuration**

Edit parameters for ARM9

Block Documentatio... 🍞 Mapping of ARM9 CPU architecture parameters to generic CPU Please NOTE that this is not goldenized and is only for Demo purpose. Architecture\_Name: Board Name Processor Name: Processor Name /\* First row contains Column Names. \*/ Processor Setup: Parameter\_Name Parameter\_Value Processor\_Instruction\_Set: ARM INSTR Micro Architecture details – Number Number\_of\_Registers: 16 /\* active registers being processed. total reg = 31 \*/ of Registers, ROB size, Number of Processor\_Speed\_Mhz: Processor\_Speed 200 /\* switch between internal pipeline stages \*/ Context\_Switch\_Cycles: Registers 100 /\* This cab be assumed. Real ARM data ? \*/ Instruction\_Queue\_Length: 5 /\* after 5'th stage is implemeted \*/ Number\_of\_Pipeline\_Stages: Number\_of\_INT\_Execution\_Units: 2 /\* 1 exection unit 1 coproc unit \*/ Hit\_Ratio by Number\_of\_FP\_Execution\_Units: 0 /\* no particular FP units \*/ Number\_of\_Cache\_Execution\_Units: 2 /\* I-cache and D-cache \*/ {Cache\_Speed\_Mhz=Processor\_Speed, Size\_KBytes=I\_Cache\_Size, Words\_per\_Cache\_Line=8, Hit\_Ratio=0.4, Cache\_Miss\_Name=Cache} I 1: default will be D 1: {Cache\_Speed\_Mhz=Processor\_Speed, Size\_KBytes=D\_Cache\_Size, Words\_per\_Cache\_Line=8, Hit\_Ratio=0.6, Cache\_Miss\_Name=Cache} 0.99 /\* Pipeline stages in ARM \*/ Pipeline\_Stages: Stage\_Name Execution Location Condition Action 1\_FETCH  $I_1$ instr none /\* Fetch \*/ 2 DECODE I\_1 wait none /\* Decode \*/ 3 DECODE : /\* Write \*/ none none exec 3\_DECODE /\* Read \*/ none exec none 3 EXECUTE ; /\* Execute ARM instr \*/ ARM exec none /\* 3\_EXECUTE Co\_Processor\_Name task VPU Execute MOVE instr \*/ Mention next l evel 4\_MEMORY ARM wait none : /\* Wait for ARM instr \*/ /\* 4\_MEMORY Wait for MOVE instr \*/ Co\_Processor\_Name wait none Cache to be 5\_WRITE\_BACK D\_1 : /\* Wait for Mem transaction \*/ write none accessed in case of Enable Hello Messages:  $\checkmark$ Processor Bits: 32 misses

#### **Processor Instruction Set**

Processor name

| le Edit | Halp   |       |          |                   |              |                       |                                                       |                                                  |                              |

|---------|--------|-------|----------|-------------------|--------------|-----------------------|-------------------------------------------------------|--------------------------------------------------|------------------------------|

|         |        | ructi | lon Set  | or File Path. */  |              |                       |                                                       |                                                  |                              |

| 2       |        |       |          |                   |              |                       |                                                       | begin execUnit_config                            | 16                           |

| Mn      | iew Ra | Rb R  | Rc Rd Re | e Rf Rg Rh ; /* I | abel */      |                       |                                                       | Queue_Size INT_1<br>Queue Size INT 2             | 16         ;<br>16         ; |

|         |        |       |          | COSIMD LDSTR ;    | ,            |                       |                                                       | Queue Size INT 3                                 | 16 ;                         |

|         |        |       | 10 1111  | JODIN HUDIN ,     |              |                       | Execution and Load                                    | Queue_Size INT_4                                 | 16 ;                         |

|         |        |       |          |                   |              |                       | Store Units within                                    | Queue_Size INT_5                                 | 16 ;                         |

|         |        |       |          |                   |              |                       | -                                                     | Queue_Size FP_1                                  | 16 ;                         |

| AL      |        |       | _        |                   |              | v, Simple ALU */      | RISCV and the                                         | Queue_Size FP_2<br>Queue_Size INT_6              | 16 ;<br>12 ;                 |

| FP      | NEOSI  | MD FP | 2_1      | ; /*Floating      | point/NEON/  | ASIMD instruction     | * <sup>/</sup> corresponding                          | Queue_Size INT_7                                 | 12 ;                         |

| LD      | STR    | IN    | NT_4     | ; /*Load/Sto      | re instructi | ons*/                 |                                                       | end execUnit_config                              | ·                            |

|         |        |       |          |                   |              |                       | instruction groups                                    | _ 0                                              |                              |

|         |        |       |          |                   |              | -                     | they execute                                          |                                                  |                              |

| be      | egin s | ize_c | config   |                   | ;            |                       | 5                                                     |                                                  |                              |

| R       | lead   | 5     | 128      | INT_4[1:2]        | ;            | begin INT_1           | ; /* Group */                                         |                                                  | <u> </u>                     |

| R       | lead   | 5     | 64       | INT_4[3:7]        | ;            | ADD 2<br>SUB 2        | i<br>i                                                |                                                  |                              |

| R       | lead   | 5     | 32       | INT 4[8:16]       | ;            | *b 2<br>MUL 4         | ;                                                     | _                                                | Queue Size                   |

| R       | lead   | 5     | 16       |                   | ;            | DIV 4<br>LDR 1        |                                                       | Instruction Group                                | for each                     |

| R       | lead   | 5     | 8        | INT 4[19:20]      | ;            | LDR I<br>LDUR 1       |                                                       |                                                  |                              |

|         | Irite  | 5     | 128      | INT_4[21:22]      | ;            | STR 1<br>end INT 1    |                                                       |                                                  | Instruction                  |

|         | Irite  |       | 64       | INT_4[23:27]      | ;            | begin FP 1            | ; /* Group */                                         |                                                  | Group                        |

| W       | Irite  | 5     | 32       | INT 4[28:35]      | ;            | FADD 2<br>FSUB 2      |                                                       |                                                  | •                            |

| W       | Irite  | 5     | 16       | sh                | ;            | FMUL 4 8<br>FDIV 4 12 |                                                       |                                                  |                              |

| W       | Irite  | 5     | 8        | sb                | ;            | end FP_1              | ;                                                     |                                                  |                              |

| en      | nd siz | e_con | nfig     |                   | ;            |                       |                                                       |                                                  |                              |

|         |        | _     |          |                   |              | The entry FADD 2      | ; means that the instruction "FADD" will take 2 cycle | s to complete execution (Without including the I | _Cache                       |

Instruction width in bits can vary for different load/store instructions

#### The entry FADD 2 ; means that the instruction "FADD" will take 2 cycles to complete execution (Without including the I\_Cache access latency and pipeline transfer latency).

The entry FMUL 4 8 ; means that the instruction FMUL can take a random delay cycle between 4 and 8 cycles to complete execution.

#### Example of Pipeline usage

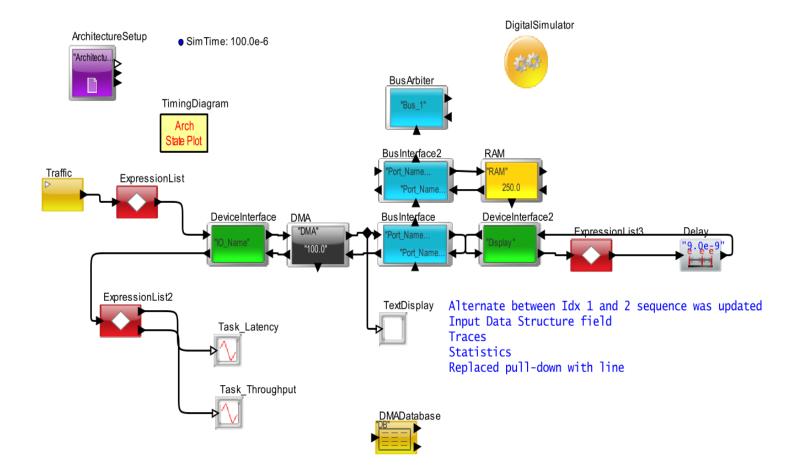

## DMA BLOCK AND ITS USAGE

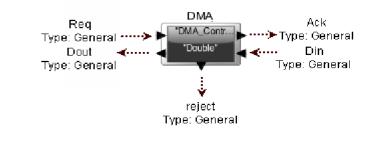

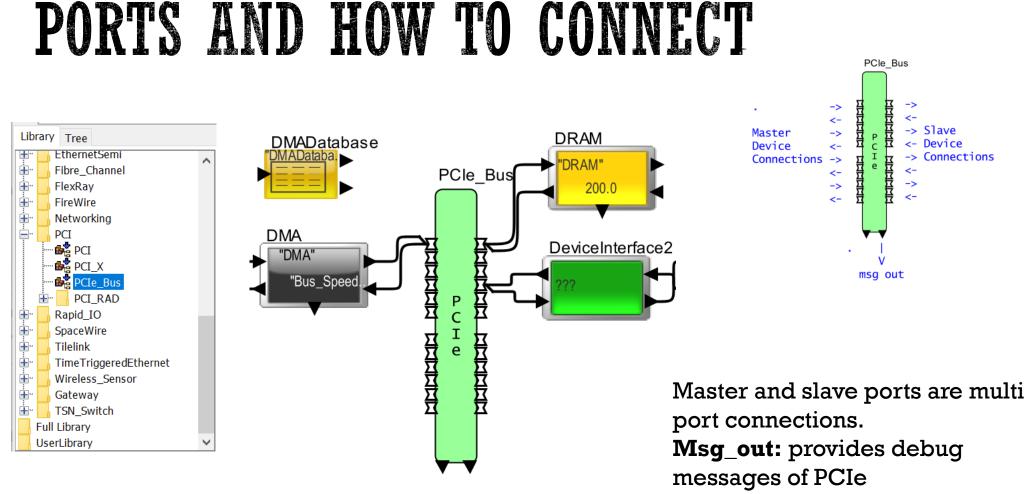

# PORTS AND HOW TO CONNECT?

- 1. **Req port** receives request from the source (Traffic generator in this case). It will be connected to DeviceInterface

- 2. Ack port will have transactions received with additional fields like Time\_Array, Trace\_Array useful for debug

- **3.** Ack and Din are connected to the output blocks via DeviceInterface or directly

- Dout carries response from output devices like Memory.

Connected to Bus,

DeviceInterface or Memory

- 5. Dout will have Task\_Latency and Task\_Throughpout as additional fields

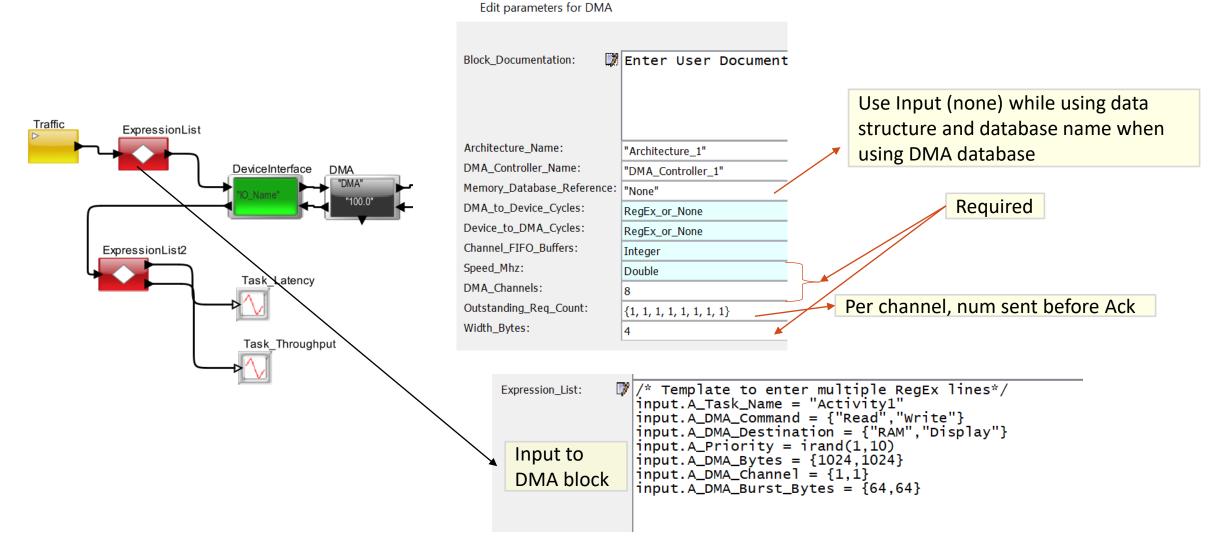

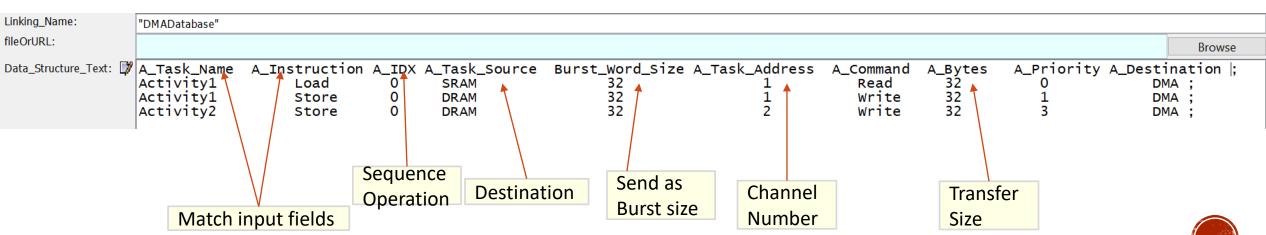

#### DMA – DEFINING ACTIONS USING DATA STRUCTURE

If the user wants to define actions for the DMA from Data structure fields, then above fields are necessary

#### USING THE DWA DATABASE

#### **DMA Controller Block**

## DMA – DEMO MODELS AND RESULTS

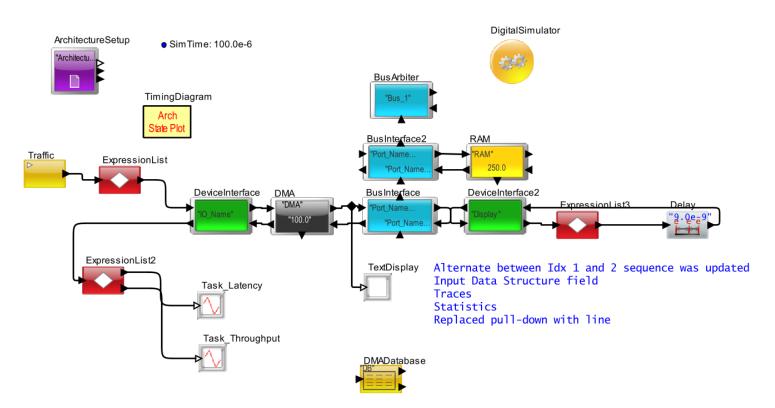

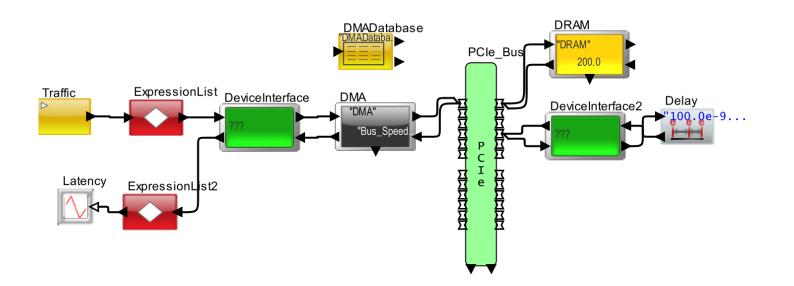

# MODEL SHOWCASING DS FIELDS AS WELL AS DMA DATABASE OPTION

#### **Model Location :**

\$VS/doc/Training\_Material/Tutorial/Architecture/DMA/DMA\_Demo\_Model\_Field\_n\_DB.xml

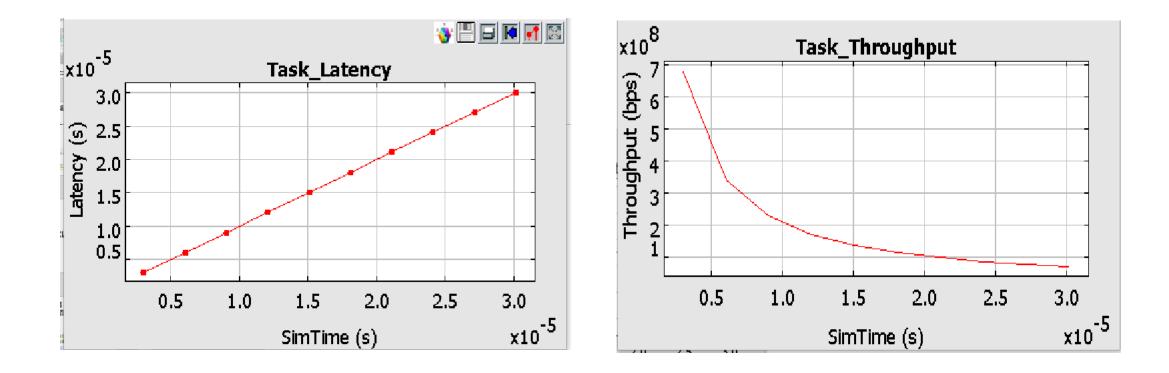

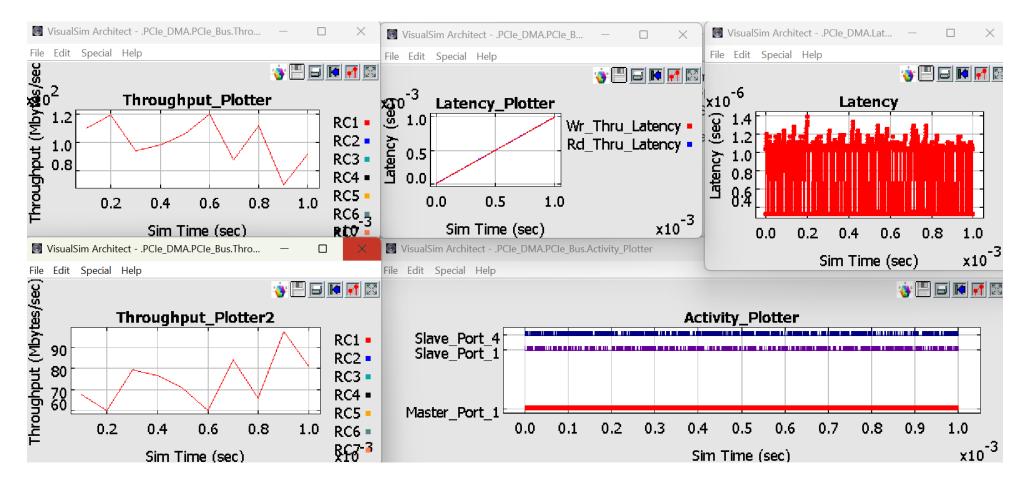

#### **RESULTS FOR THE PREVIOUS MODEL**

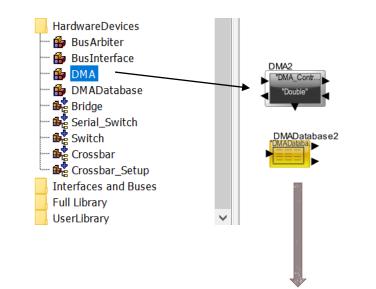

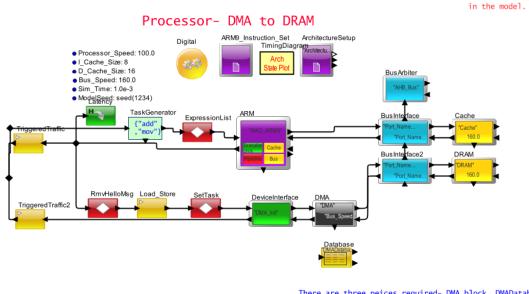

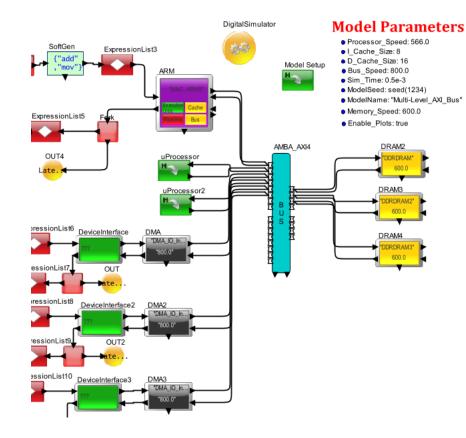

### CONNECTING PROCESSOR – DMA – DRAM

There are three peices required- DMA block, DMADatabase block and the entry in the processor: Memory\_Database\_Reference: DMADatabase, where DMADatabase is the name of the Database block containing the DMA Task activity it is best to connect the DMA to one of the ports of the processor either directly or via a Bus.

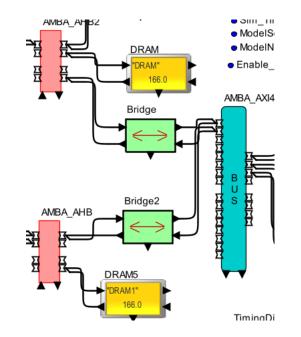

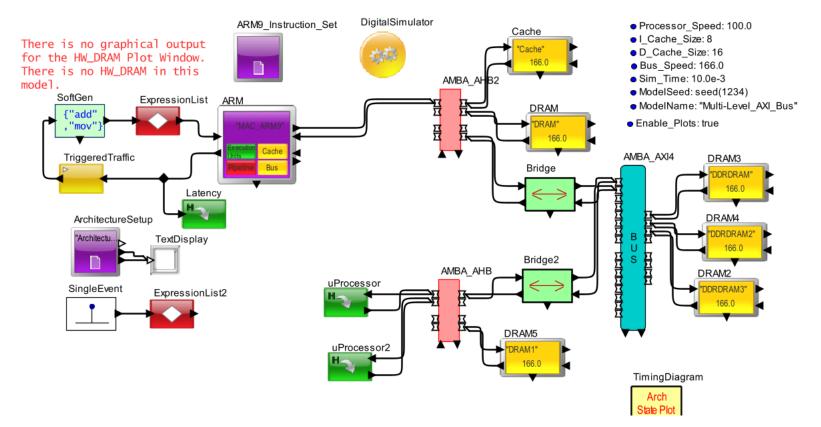

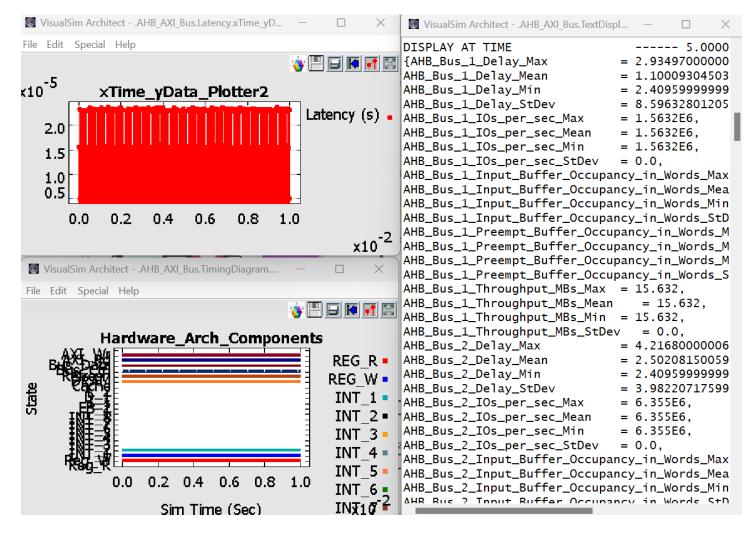

There is no graphical output to the HW\_DRAM Plot. This is not used

**Model Location :** \$VS/doc/Training\_Material/Tutorial/Architecture/DMA/Processor\_DMA.xml

#### **RESULTS FOR THE PREVIOUS MODEL**

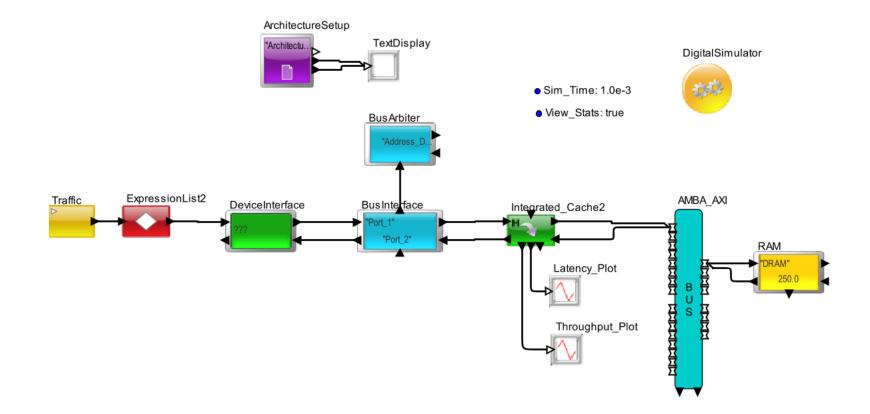

## BUS ARBITER AND BUS INTERFACE BLOCKS AND ITS USAGE

# PORTS AND HOW TO CONNECT

#### **KEY CONFIGURATION**

Edit parameters for BusArbiter2

| List all devices connected via<br>this port. Index is in order of<br>name. Port 1. Port 2 otc.<br>Vidth_Bytes:<br>Arbiter_Mode:<br>Split_Retry_Flag:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                          |  |                                    |                               |             |   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--|------------------------------------|-------------------------------|-------------|---|

| List all devices connected via this port. Index is in order of pame. Port 1. Port 2 arts and content of the pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 2 arts and content of pame. Port 2 arts a |                          |  | Block_Documentation:               | Enter User Documentatio       | on Here     |   |

| List all devices connected via this port. Index is in order of pame. Port 1. Port 2 arts and content of the pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 2 arts and content of pame. Port 2 arts a |                          |  |                                    |                               |             |   |

| List all devices connected via this port. Index is in order of pame. Port 1. Port 2 arts and content of the pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 2 arts and content of pame. Port 2 arts a |                          |  |                                    |                               |             |   |

| List all devices connected via this port. Index is in order of pame. Port 1. Port 2 arts and content of the pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 1. Port 2 arts and content of pame. Port 2 arts and content of pame. Port 2 arts a |                          |  |                                    |                               |             |   |

| Required       Bus_Name:       Cluster_Name+"_DSU_Cache_Bus"       Unique Name         Bus_Speed_Mhz:       Core_Speed_Mhz         Burst_Size_Bytes:       100         Round_Robin_Port_Array:       ("Port_1", "Port_2"}         Devices_Attached_to_Slave_by_Port:       1"}, {"Device_3"}, {"Device_4"}, {"Device_5"}, {"Device_5"}, {"Device_7"}, {"Device_4"}         List all devices connected via this port. Index is in order of name       Split_Retry_Flag:       Image: Core_Speed_Mhz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                          |  | Architecture_Name:                 | "Architecture_1"              |             |   |

| Required       Bus_Speed_Mhz:       Core_Speed_Mhz         Burst_Size_Bytes:       100         Round_Robin_Port_Array:       ("Port_1", "Port_2")         Devices_Attached_to_Slave_by_Port:       1"), {"Device_2"}, {"Device_3"}, {"Device_4"}, {"Device_5"}, {"Device_6"}, {"Device_7"}, {"Device_5"}, {"Device_7"}, {"Device_5"}, {"Device_5"}                                                                                                                                                           |                          |  | _explanation:                      | HardwareDevices->BusArbiter   |             | 1 |

| Interprised       Burst_Size_Bytes:       100         Round_Robin_Port_Array:       ("Port_1", "Port_2")         Devices_Attached_to_Slave_by_Port:       1"}, {"Device_3"}, {"Device_4"}, {"Device_5"}, {"Device_6"}, {"Device_7"}, {"Device_1"         List all devices connected via this port. Index is in order of       Arbiter_Mode:       FCFS         Split_Retry_Flag:       ✓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                          |  | Bus_Name:                          | Cluster_Name+"_DSU_Cache_Bus" | Unique Name |   |

| Round_Robin_Port_Array:       {"Port_1", "Port_2"}         Devices_Attached_to_Slave_by_Port:       !", {"Device_3"}, {"Device_4"}, {"Device_5"}, {"Device_6"}, {"Device_7"}, {"Device_4"}         List all devices connected via this port. Index is in order of name. Port_1 Port_2 atc.       Arbiter_Mode:       FCFS         Split_Retry_Flag:       Image: Split_Retry_Flag:       Image: Split_Retry_Flag:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Required                 |  | Bus_Speed_Mhz:                     | Core_Speed_Mhz                |             |   |

| List all devices connected via<br>this port. Index is in order of<br>pame. Port 1. Port 2 otc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                          |  | Burst_Size_Bytes:                  |                               |             |   |

| List all devices connected via<br>this port. Index is in order of<br>pame. Port 1. Port 2 otc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                          |  | Round_Robin_Port_Array:            |                               |             |   |

| List all devices connected via<br>this port. Index is in order of Split_Retry_Flag:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                          |  | Devices_Attached_to_Slave_by_Port: |                               |             |   |

| this port. Index is in order of Split_Retry_Flag:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                          |  | ▲ Width_Bytes:                     | {16,64} <b>{Read, Write}</b>  |             |   |

| name Bort 1 Bort 2 otc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                          |  | Arbiter_Mode:                      | FCFS                          |             | × |

| name-Port 1. Port 2 etc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                          |  | Split_Retry_Flag:                  | $\checkmark$                  |             |   |

| Enable_Plots:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | name- Port_1, Port_2 etc |  | Enable_Plots:                      |                               |             |   |

\_

$\times$

Alternate Read and Write operation Bus will perform one functionality at a time

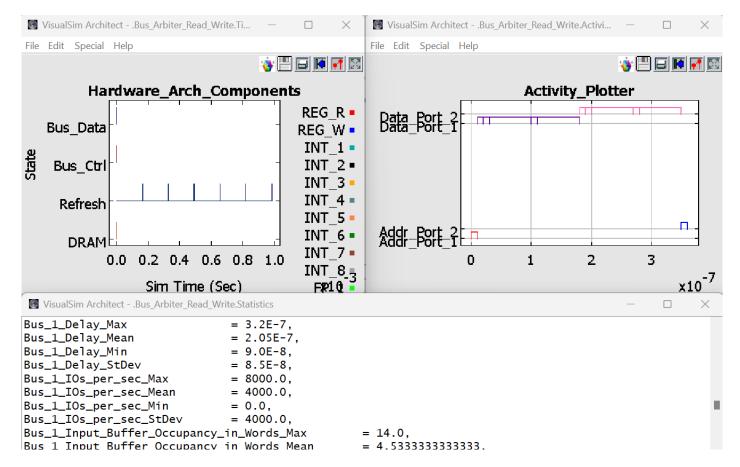

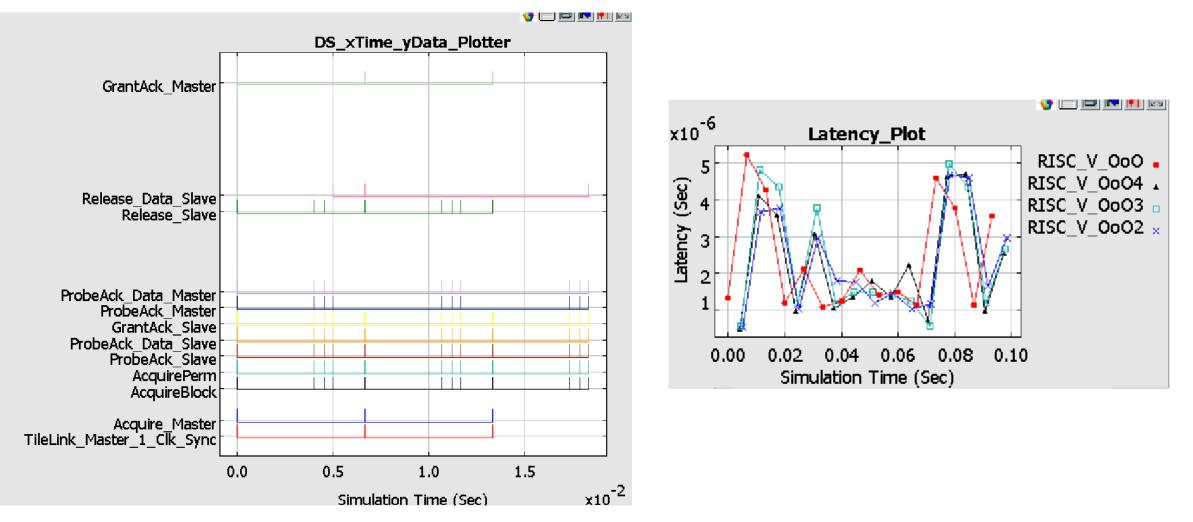

# **RESULTS FOR THE PREVIOUS MODEL**

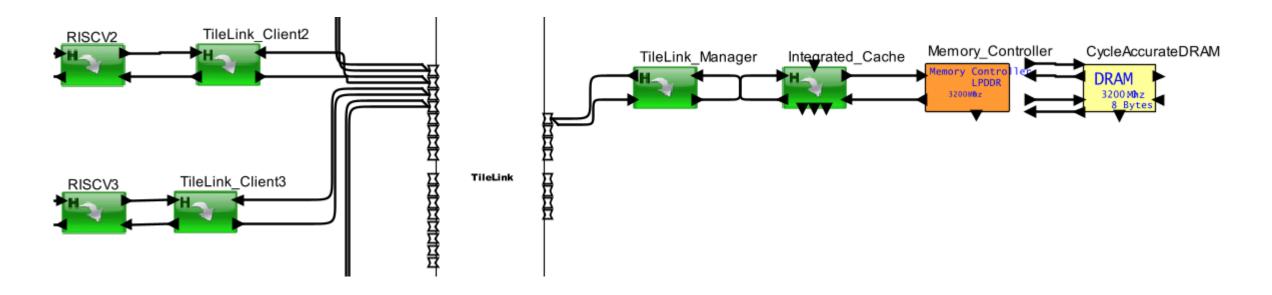

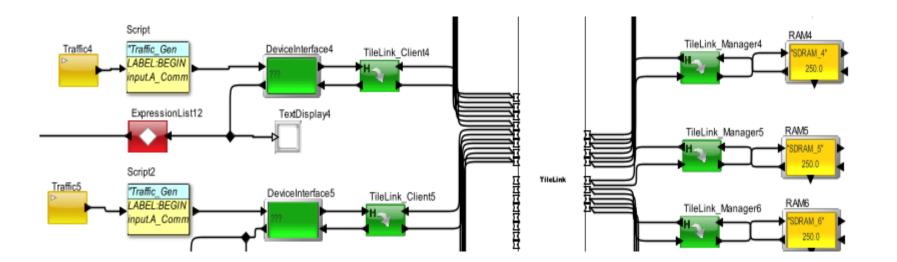

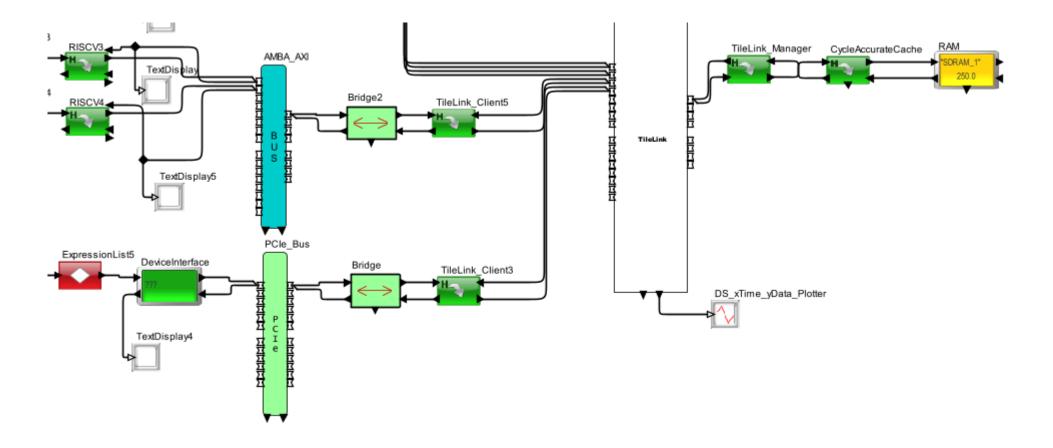

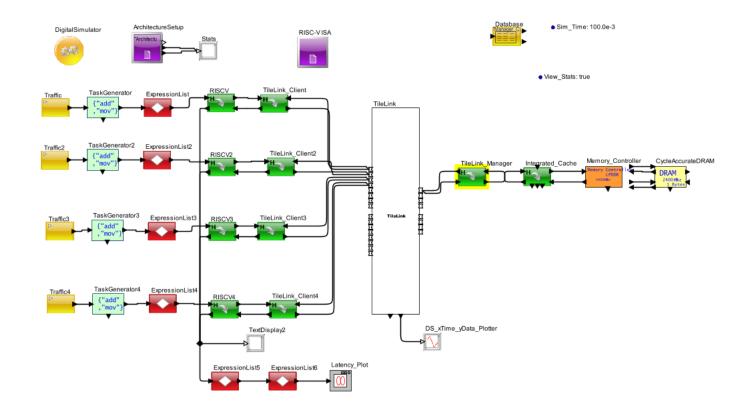

#### TILELINK AND ITS USAGE

# PORTS AND HOW TO CONNECT?

1. Source (master devices that request data) like Processor and DMA (standard blocks) have to be connected to the master ports via TileLink\_Client (Library -- > Interfaces and Buses --> TileLink --> TileLink\_Client)

## CONTINUED

2. If the Master device is designed with simple library block (as logic) then user has to include Device Interface block to provide the interface with master.

#### CONTINUED

3. If the TileLink\_Client is connecting to another BUS like PCIe or AMBA-AXI, then the user has to use a Bridge (Library --> HardwareDevices --> Bridge)

### KEY CONFIGURATION

| Edit parameter | s for TileLink |

|----------------|----------------|

|----------------|----------------|

| TileLink_Name:                                                                                 | "TileLink"                                                                                            |

|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| TileLink_Speed_Mhz:                                                                            | 1000.0                                                                                                |

| TileLink_Cycle_Time:                                                                           | (1.0E-6/TileLink_Speed_Mhz)                                                                           |

| Bus_Width:                                                                                     | 8                                                                                                     |

| Number_Masters:                                                                                | 4                                                                                                     |

| Number_Slaves:                                                                                 | 1                                                                                                     |

| Slave_Speeds_Mhz:                                                                              | {TileLink_Speed_Mhz, TileLink_Speed_Mhz, TileLink_Speed_Mhz, TileLink_Speed_Mhz, TileLin              |

| $\label{eq:cycles_for_RdReq_WrReq_RdData_WrData:} Extra_Cycles_for_RdReq_WrReq_RdData_WrData:$ | {0, 0, 0, 0, 0, 0, 0, 0}                                                                              |

| Devices_Attached_to_Slave_by_Port:                                                             | {{"L2","SDRAM_1"},{"SDRAM_2"},{"SDRAM_3"},{"SDRAM_4"},{"SDRAM_5"},{"SDRAM_6"}                         |

| Master_First_Word_Flag:                                                                        | true                                                                                                  |

| DEBUG:                                                                                         | false                                                                                                 |

| Ports_to_Plot:                                                                                 | {1,1} /* master n, slave m, 0 disables */                                                             |

| Managers_Attached_to_Slave_by_Port:                                                            | {{" <u>Manager1"},{"M</u> anager2"},{"Manager3"}, <b>,</b> "Manager4"},{"Manager5"},{"Manager6"},{"Ma |

| Architecture_Name:                                                                             | "Architecture_1"                                                                                      |

|                                                                                                |                                                                                                       |

|                                                                                                |                                                                                                       |

| Commit Add Ren                                                                                 | nove Restore Defaults Preferences Help Cancel                                                         |

|                                                                                                |                                                                                                       |