# REFERENCE GUIDE

# INTRODUCTION TO THE CONCEPTS AND USING VISUALSIM

## MIRABILIS DESIGN INC.

2010 El Camino Real, #1061

Santa Clara, CA 95050

www.mirabilisdesign.com

info@mirabilisdesign.com

©2003-2022 Mirabilis Design Inc. All rights reserved.

The information contained herein is subject to change without notice. While every reasonable effort was made to ensure the completeness and correctness of this document, Mirabilis Design Inc. makes no warranty of any kind with regard to this material, including but not limited to any implied warranties. Mirabilis Design Inc. shall not be liable for errors or omissions contained herein or for any damages relating to the use of this material.

VisualSim, SmartBlocks and SmartMachine are registered trademark of Mirabilis Design Incorporated.

Java and all Java-related titles are trademarks or registered trademarks of Sun Microsystems in the United States and other countries. All other brand or product names may be trademarks of their respective holders.

This document is protected by US and International copyright laws. No part of this document may be reproduced in any manner without prior written consent of Mirabilis Design Inc.

Mirabilis Design Inc.

2010 El Camino Real, #1061

Santa Clara, CA 95050

# **TABLE OF CONTENTS**

| 1 SCO  | PPE AND PURPOSE OF THE DOCUMENT       | 19 |

|--------|---------------------------------------|----|

| 1.1    | INTRODUCTION                          | 19 |

| 1.2    | Scope                                 | 19 |

| 2 STA  | RTING VISUALSIM                       | 20 |

| 2.1    | RUNNING VISUALSIM ARCHITECT           | 20 |

| 2.2    | RUNNING VISUALSIM POST PROCESSOR      | 20 |

| 2.3    | RUNNING VISUALSIM EXPLORER            | 20 |

| 3 VISU | JALSIM PRODUCTS, EDITORS, AND TOOLS   | 22 |

| 3.1    | BLOCK DIAGRAM EDITOR                  | 22 |

| 3.1.1  | Menu Commands                         | 22 |

| 3.1.2  | Details of Menu and Toolbar Operation | 28 |

| 3.1.3  | Listeners                             | 37 |

| 3.1.4  | Folders and Tree                      | 38 |

| 3.2    | TEXT EDITOR AND LISTENER WINDOWS      | 38 |

| 3.2.1  | Introduction                          | 38 |

| 3.2.2  | Commands                              | 38 |

| 3.2.3  | Quick Key Commands                    | 38 |

| 3.3    | PLOTTERS AND VISUALSIM POST PROCESSOR | 39 |

| 3.3.1  | Introduction                          | 39 |

| 3.3.2  | Post Processor Window                 | 41 |

| 3.3.3  | Using Plot                            | 42 |

| 3.3.4  | Commands Configuring the Axes         | 45 |

| 3.3.5  | Commands for Plotting Data            | 47 |

| 3.4    | VISUALSIM POST PROCESSOR              | 50 |

| 3.4.1  | Introduction                          | 50 |

| 3.4.2  | Key Features                          | 50 |

| 3.4.3  | Quick Key Command                     | 50 |

| 3.4.4  | Usage                                 | 51 |

| 3.4.5  | VisualSim Architect Models            | 52 |

|   | 3.4.6  | Usage                                  | 53 |

|---|--------|----------------------------------------|----|

|   | 3.4.7  | Activity Menu                          | 53 |

|   | 3.4.8  | XML Menu                               | 54 |

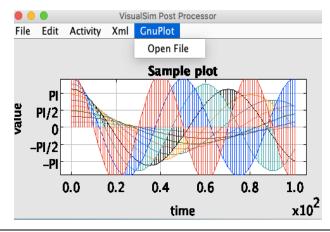

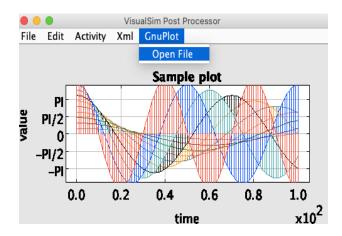

|   | 3.4.9  | GnuPlot Menu                           | 58 |

|   | 3.4.10 | Post Processor-> Comparator            | 60 |

|   | 3.4.11 | Packaging and Archiving                | 64 |

|   | 3.5    | ICON EDITOR                            | 64 |

|   | 3.6    | EXPRESSION EVALUATOR                   | 64 |

|   | 3.7    | SIMULATION COCKPIT                     | 66 |

|   | 3.7.1  | Operation                              | 66 |

|   | 3.7.2  | Listen to the Manager and Simulator    | 67 |

|   | 3.7.3  | Stop and Resume                        | 67 |

|   | 3.7.4  | Simulation Parameters                  | 68 |

|   | 3.7.5  | Plot viewers in the Simulation Cockpit | 68 |

| 4 | BLOC   | CKS                                    | 69 |

|   | 4.1    | BLOCK EXECUTION SEMANTICS              | 69 |

|   | 4.2    | BLOCK LAYOUT                           | 70 |

|   | 4.3    | BLOCK CONTEXT MENU                     | 71 |

|   | 4.3.1  | Customize                              | 71 |

|   | 4.3.2  | Customize Name                         | 73 |

|   | 4.3.3  | Get Documentation                      | 73 |

|   | 4.3.4  | Send to Back                           | 74 |

|   | 4.3.5  | Bring to Front                         | 74 |

|   | 4.3.6  | Save Block in Library                  | 74 |

|   | 4.3.7  | Listen to Block                        | 74 |

|   | 4.3.8  | Set Breakpoint                         | 75 |

|   | 4.3.9  | Convert to Class                       | 75 |

|   | 4.3.10 | Create Instance                        | 75 |

|   | 4.3.11 | Create Subclass                        | 75 |

|   | 4.3.12 | Convert to Instance                    | 75 |

|   | 4.3.13 | Open Block                             | 75 |

|   | 4.3.14 | Open Instance                          | 75 |

|   |        | Open motanee                           | •  |

|   | 4.3.16      | Remove Custom Icon                                   | /6  |

|---|-------------|------------------------------------------------------|-----|

| 4 | 1.4         | SETTING UP A BLOCK                                   | 76  |

|   | 4.4.1       | Blocks Overview                                      | 76  |

|   | 4.4.2       | Updating Parameters and adding additional parameters | 77  |

|   | 4.4.3       | Updating Ports and adding additional ports           | 77  |

|   | 4.4.4       | Setting Port Types                                   | 78  |

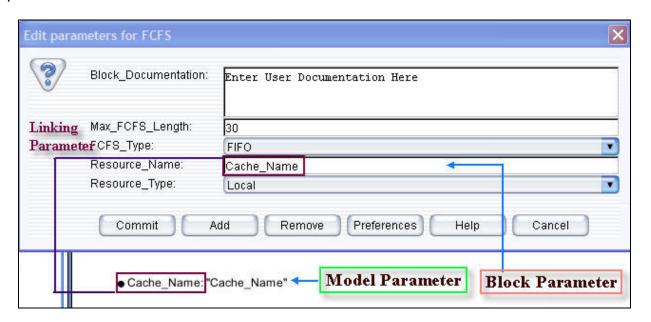

|   | 4.4.5       | Linking Parameters                                   | 79  |

|   | 4.4.6       | Block Documentation                                  | 80  |

|   | 4.4.7       | Icon Display value                                   | 80  |

|   | 4.4.8       | Tooltip value                                        | 80  |

|   | 4.4.9       | Creating Generic Port Icon                           | 80  |

| 5 | HIER        | ARCHICAL BLOCK SEMANTICS                             | 82  |

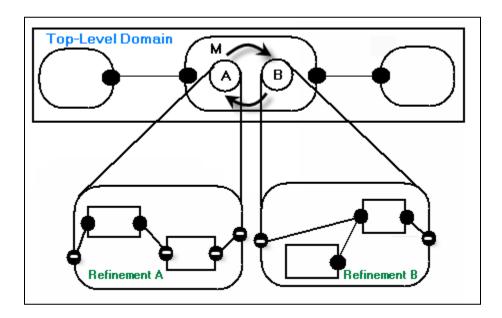

| 5 | 5.1         | USING HIERARCHICAL BLOCKS                            | 82  |

| 5 | 5.2         | MODEL EXECUTION SEMANTICS                            | 84  |

| 5 | 5.3         | MODEL EXECUTION FLOWCHART                            | 85  |

| 5 | 5.4         | CREATE SUB-MODEL                                     | 86  |

| 6 | DYNA        | AMIC INSTANTIATION                                   | 87  |

| 6 | 5.1         | INTRODUCTION                                         | 87  |

| 6 | 6.2         | EXAMPLE                                              | 88  |

|   | 6.2.1       | How To                                               | 89  |

|   | 6.2.2       | Requirements                                         | 89  |

|   | 6.2.3       | Example of the Dynamic Instantiation                 | 90  |

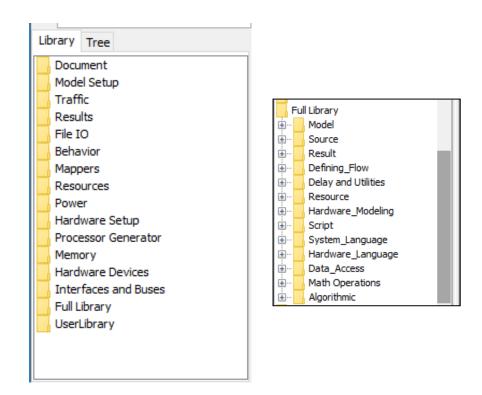

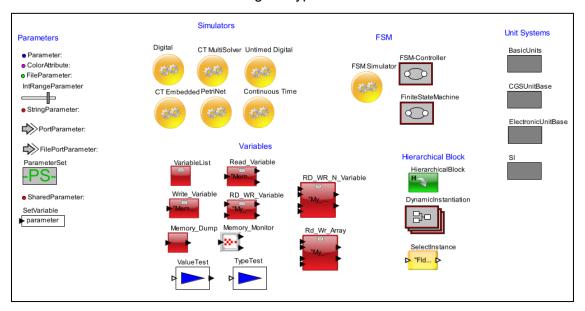

| 7 | LIBR        | ARY FOLDER ORGANIZATION                              | 92  |

| 7 | <b>7</b> .1 | MODEL / DOCUMENT / MODELSETUP                        | 92  |

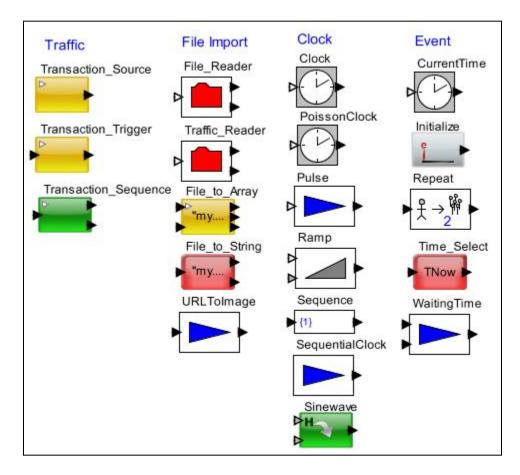

| 7 | <b>7</b> .2 | TRAFFIC / SOURCE                                     | 93  |

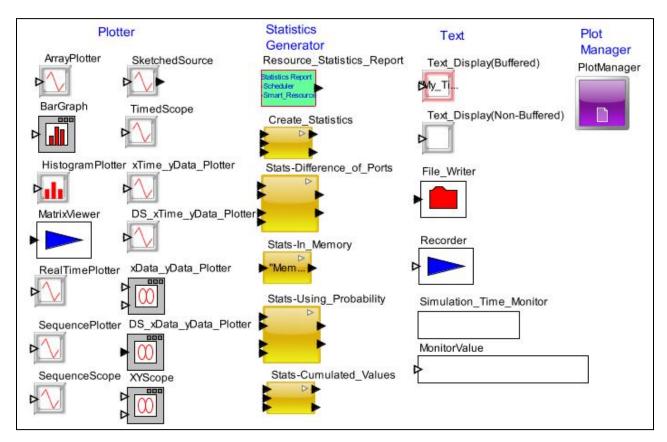

| 7 | 7.3         | RESULTS                                              | 94  |

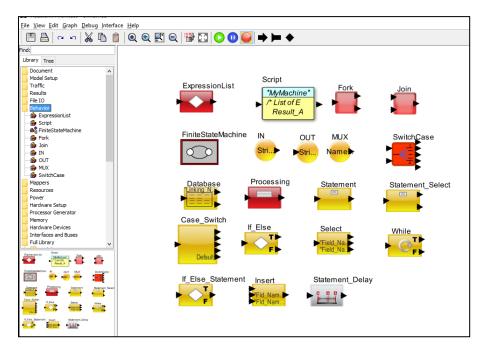

| 7 | <b>7</b> .4 | BEHAVIOR                                             | 95  |

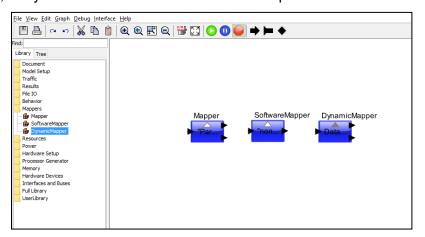

| 7 | <b>7</b> .5 | MAPPERS                                              | 97  |

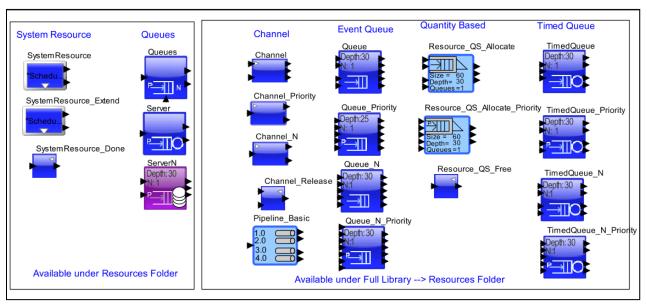

| 7 | <b>'</b> .6 | RESOURCES                                            | 97  |

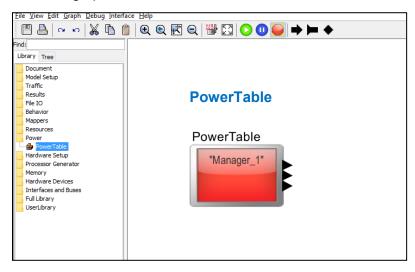

| 7 | <b>7</b> .7 | Power                                                | 99  |

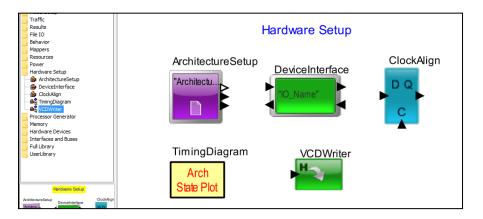

| 7 | <b>'</b> .8 | HARDWARE SETUP                                       | 99  |

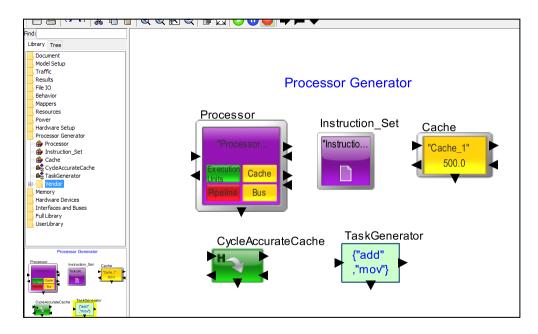

| 7 | 7 9         | PROCESSOR GENERATOR                                  | 100 |

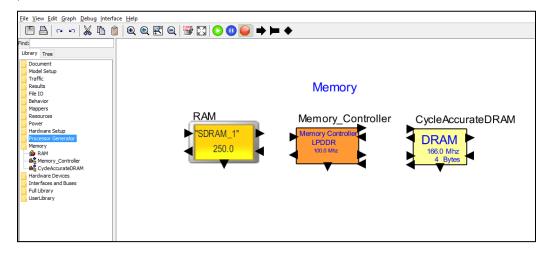

| 7.10    | MEMORY                                         | 101 |

|---------|------------------------------------------------|-----|

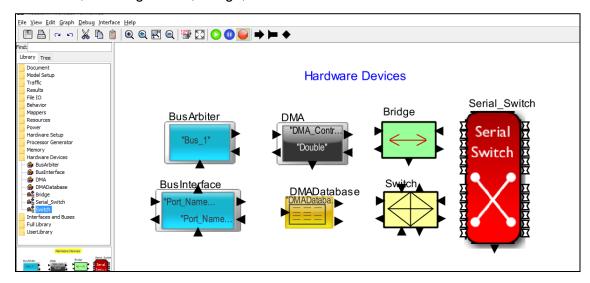

| 7.11    | HARDWARE DEVICES                               | 102 |

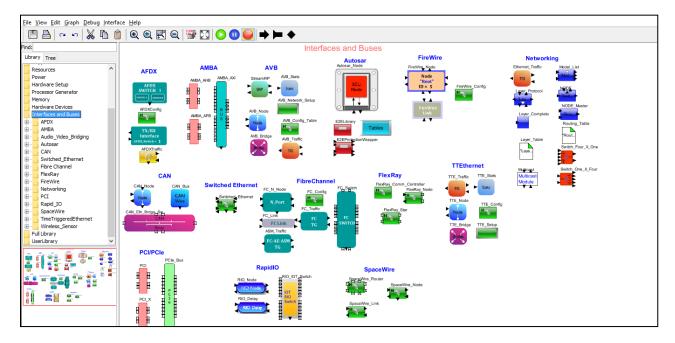

| 7.12    | INTERFACES AND BUSES                           | 102 |

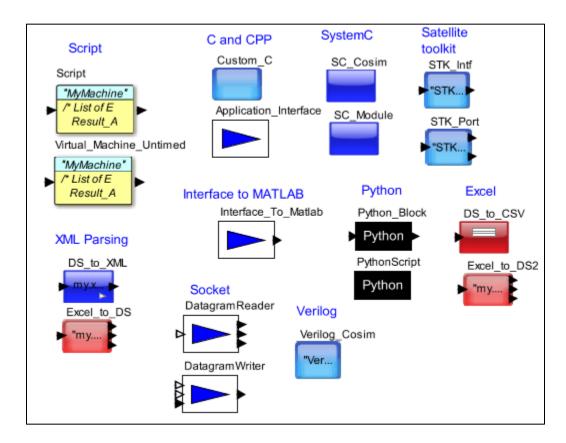

| 7.13    | SYSTEM_LANGUAGE                                | 103 |

| 7.14    | HARDWARE LANGUAGE                              | 103 |

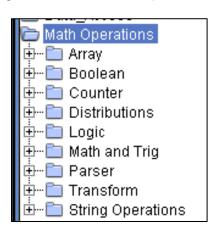

| 7.15    | MATH_OPERATIONS                                | 104 |

| 7.16    | ALGORITHMIC                                    | 105 |

| 7.17    | USERLIBRARY                                    | 105 |

| 8 BLO   | CK, SUB-MODELS (CLASSES) AND INHERITANCE       | 106 |

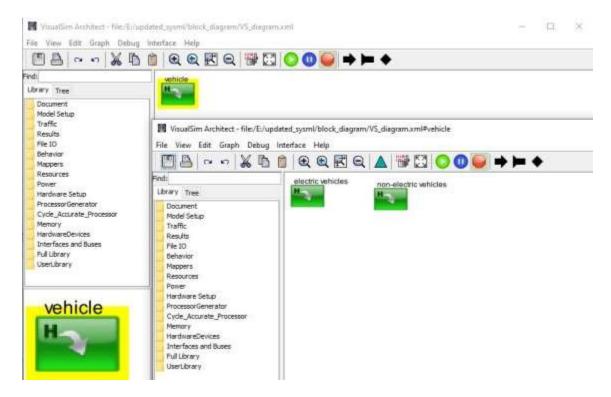

| 8.1     | INTRODUCTION                                   | 106 |

| 8.2     | EXAMPLE OF CLASSES                             | 107 |

| 8.2.1   | Overriding Parameter Values in Instances       | 114 |

| 8.2.2   | Subclass and Inheritance                       | 115 |

| 8.2.3   | Sub-Models                                     | 118 |

| 9 CLA   | SSES AND LIBRARIES                             | 120 |

| 9.1     | CREATE CLASS- SEQUENCE OF OPERATIONS           | 120 |

| 9.2     | CREATE LIBRARY AND INSTANTIATE IN USER_LIBRARY | 121 |

| 9.3     | EXAMPLE OF CREATING A NEW CLASS BLOCK          | 121 |

| 9.4     | ANNOTATING THE CLASS                           | 124 |

| 9.5     | INSTANTIATING THE CLASS IN MODEL               | 124 |

| 9.6     | TEST THE NEW CLASS BLOCK:                      | 125 |

| 10 LIBR | RARY MANAGEMENT                                | 127 |

| 10.1    | INTRODUCTION                                   | 127 |

| 10.2    | VERSION CONTROL                                | 127 |

| 10.3    | LIBRARY STORAGE                                | 127 |

| 10.4    | USER LIBRARY                                   | 129 |

| 11 XML  | DETAILS AND FILE PARSING                       | 130 |

| 11.1    | INTRODUCTION                                   | 130 |

| 11.2    | Toplogy                                        | 132 |

| 11.3    | RELATION GROUPS                                | 132 |

| 11.4    | SPECIFICATION OF A MODEL                       | 133 |

| 11. <del>4</del> .1 | Data Organization                              | 133 |

|---------------------|------------------------------------------------|-----|

| 11.5                | OVERVIEW OF XML                                | 135 |

| 11.6                | Names and Classes                              | 135 |

| 11.7                | TOP-LEVEL ENTITIES                             | 136 |

| 11.8                | ENTITY ELEMENT                                 | 137 |

| 11.9                | PROPERTIES                                     | 138 |

| 11.10               | CLASSES                                        | 146 |

| 11.11               | INHERITANCE                                    | 148 |

| 11.12               | SIMULATORS                                     | 149 |

| 11.13               | INPUT ELEMENT                                  | 149 |

| 11.14               | ANNOTATIONS FOR VISUAL RENDERING               | 150 |

| 12 LICE             | NSE MANAGER                                    | 152 |

| 13 SIMU             | LATION TECHNOLOGY                              | 153 |

| 13.1                | INTRODUCTION                                   | 153 |

| 13.2                | MODELS OF COMPUTATION                          | 153 |

| 13.3                | SIMULATORS- HOW TO SELECT THE RIGHT ONE?       | 153 |

| 13.4                | SIMULATORS                                     | 155 |

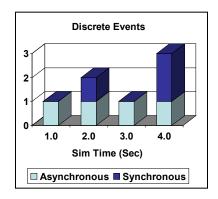

| 13.4.2              | Choosing Models of Computation                 | 159 |

| 14 BAT              | CH MODE SIMULATION EXECUTION                   | 161 |

| 14.1                | INTRODUCTION                                   | 161 |

| 14.2                | ERROR CHECKING                                 | 161 |

| 14.3                | BATCH MODE SIMULATION SCRIPT FORMAT            | 161 |

| 14.3.1              | List of Paths                                  | 163 |

| 14.3.2              | Path to save the Batch simulation results file | 163 |

| 14.3.3              | Parameter Name                                 | 164 |

| 14.3.4              | Parameter Value                                | 164 |

| 14.3.5              | Model Name                                     | 165 |

| 14.3.6              | Using Post Processor to create the batch file  | 165 |

| 14.4                | VIEWERS, PLOTERS AND TEXT DISPLAYS             | 167 |

| 14.5                | OUTPUT                                         | 168 |

| 14.5.1              | Model statistics                               | 168 |

| 1452                | Summary                                        | 168 |

|    | 14.5.3 | Saving text and Plots                          | 169 |

|----|--------|------------------------------------------------|-----|

| 15 | PAUS   | SE AND RESUME FUNCTION WITH DEBUGGING FACILITY | 170 |

| 1  | 5.1    | How to Use Pause and Resume Function           | 170 |

| 1  | 5.2    | STEPS:                                         |     |

| 16 | AUTO   | )-SAVE                                         | 171 |

| 17 | DATA   | A TYPES                                        | 172 |

| 1  | 7.1    | SCALAR AND NUMERICAL VALUES                    | 172 |

| 1  | 7.2    | STRING CONSTANTS                               | 173 |

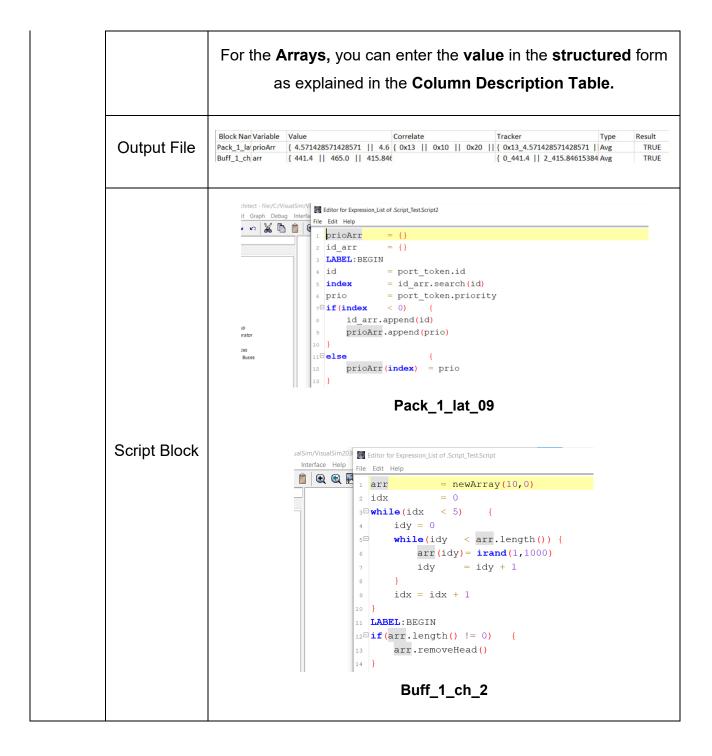

| 1  | 7.3    | Arrays                                         | 173 |

| 1  | 7.4    | MATRICES                                       | 177 |

| 1  | 7.5    | DATA STRUCTURE OR TRANSACTION OR RECORD TOKEN  | 180 |

| 1  | 7.6    | Invoking Methods                               | 182 |

| 1  | 7.7    | DEFINING FUNCTIONS                             | 183 |

| 1  | 7.8    | FIXED POINT NUMBERS                            | 186 |

| 1  | 7.9    | SPECIAL FUNCTIONS                              | 188 |

| 1  | 7.10   | DISTRIBUTIONS                                  | 189 |

| 1  | 7.11   | PROPERTY()                                     | 190 |

| 1  | 7.12   | REMAINDER()                                    | 190 |

| 1  | 7.13   | Power and Modulo                               | 191 |

| 18 | DATA   | STRUCTURES                                     | 193 |

| 1  | 8.1    | INTRODUCTION                                   | 193 |

| 1  | 8.2    | LAYOUT                                         | 193 |

| 1  | 8.3    | SUPPORTED DATA TYPES                           | 195 |

| 1  | 8.4    | PORT TYPING                                    | 196 |

| 1  | 8.5    | DATA STRUCTURE TEMPLATE LOCATION               | 196 |

| 1  | 8.6    | DATA STRUCTURE DEFINITIONS AND EXAMPLE         | 196 |

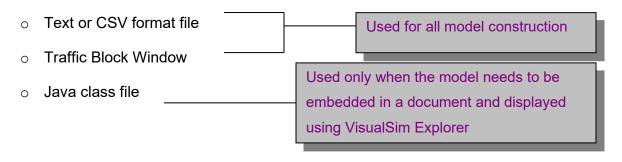

|    | 18.6.1 | Text Example                                   | 197 |

|    | 18.6.2 | Java Example                                   | 197 |

|    | 18.6.3 | Finding the Data Structure Template            | 198 |

| 1  | 8.7    | PATH DEFINITION                                | 198 |

| 1  | 8.8    | CONSTRUCTION                                   | 199 |

| 18.8.  | 1 Compiling Java Data Structure                 | 199 |

|--------|-------------------------------------------------|-----|

| 19 PRC | DCESSOR_DS                                      | 200 |

| 19.1   | Introduction                                    | 200 |

| 19.2   | USAGE OF DATA STRUCTURE FIELDS IN THE MODEL     | 203 |

| 19.3   | PROCESSOR_DS EXAMPLE                            | 206 |

| 20 PAF | RAMETERS                                        | 209 |

| 20.1   | Introduction                                    | 209 |

| 20.2   | Parameter Values                                | 209 |

| 20.3   | CREATION                                        | 210 |

| 20.4   | USING PARAMETERS                                | 210 |

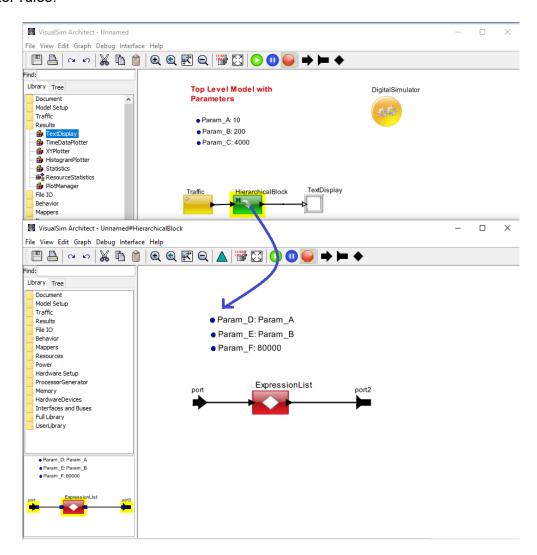

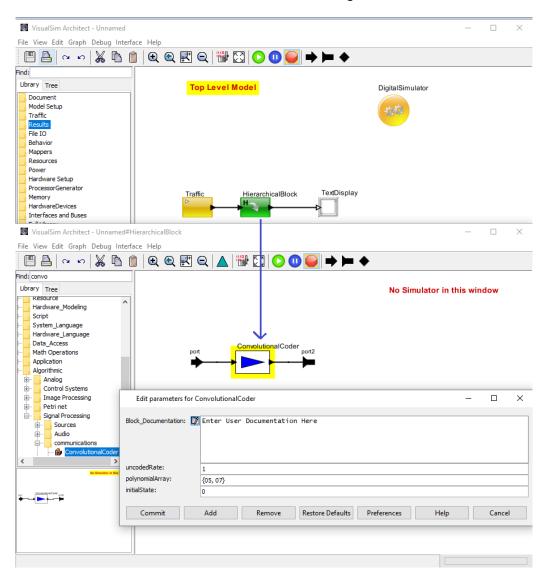

| 20.5   | LINKING PARAMETERS UP/ DOWN THE MODEL HIERARCHY | 213 |

| 20.6   | PARAMETERS AS VARIABLES                         | 214 |

| 20.7   | SHARED PARAMETERS                               | 214 |

| 20.8   | SPECIAL PARAMETERS                              | 215 |

| 20.9   | PARAMETER VALUE ON THE ICON                     | 215 |

| 21 CON | NFIGURING PORTS AND MAKING CONNECTIONS          | 217 |

| 21.1   | Introduction                                    | 217 |

| 21.2   | EDITING                                         | 217 |

| 21.3   | ADDING A PORT                                   | 220 |

| 21.4   | REMOVING PORTS                                  | 220 |

| 21.5   | POLYMORPHIC PORT TYPES                          | 220 |

| 21.6   | Ports                                           | 221 |

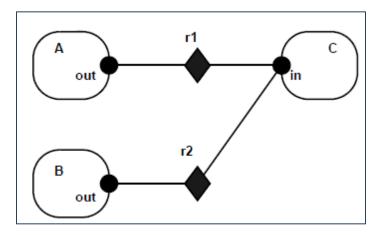

| 21.7   | RELATION AND LINK                               | 221 |

| 21.8   | POINT-TO-POINT BLOCK CONNECTIONS                | 222 |

| 21.9   | Making Connections                              | 223 |

| 21.10  | VIRTUAL CONNECTIONS                             | 223 |

| 21.11  | ADDING PARAMETERS TO LINKS AND PORTS            | 223 |

| 21.12  | CREATING GENERIC PORT ICON                      | 224 |

| 22 MOI | DEL VARIABLE                                    | 226 |

| 22.1   | Introduction                                    | 226 |

| 22.2   | VARIARI E TYPES                                 | 226 |

| 22.3   | VARIABLE DATA TYPES                                | 227 |

|--------|----------------------------------------------------|-----|

| 22.4   | Variable Names                                     | 227 |

| 22.5   | INITIALIZE VARIABLE                                | 228 |

| 22.6   | CHECKERS                                           | 229 |

| 22.7   | ACCESSING LOCAL VARIABLES                          | 230 |

| 22.8   | THINGS TO REMEMBER                                 | 230 |

| 22.9   | POINTER / REFERENCE TO A VARIABLE                  | 231 |

| 23 FIL | E PATHS                                            | 233 |

| 24 MO  | DELING LANGUAGES                                   | 234 |

| 25 DA  | TA STRUCTURES EXPRESSION LANGUAGE                  | 238 |

| 25.1   | FORMAT FOR THE STATEMENT BLOCKS                    | 241 |

| 26 DIF | FERENCES BETWEEN SCRIPT AND C PROGRAMMING          | 244 |

| 27 SCI | RIPT BLOCK                                         | 245 |

| 28 RE  | GEX LANGUAGE                                       | 248 |

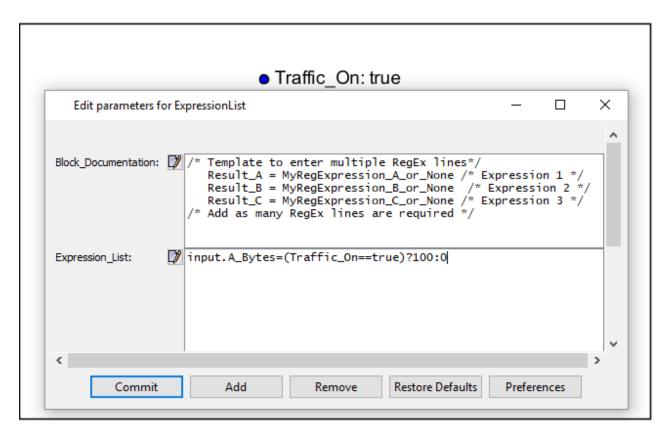

| 28.1   | COMPUTATION USING REGEX                            | 248 |

| 28.2   | CASTING AND CONVERSIONS                            | 249 |

| 28.3   | REGEX FUNCTIONS- QUEUE AND SYSTEMRESOURCE; METHODS | 250 |

| 28.3   | .1 Mapping Functions to Blocks for getBlockStatus  | 250 |

| 28.3   | .2 getBlockStatus Functions                        | 251 |

| 28.3   | .3 getBlockStatus format and example               | 251 |

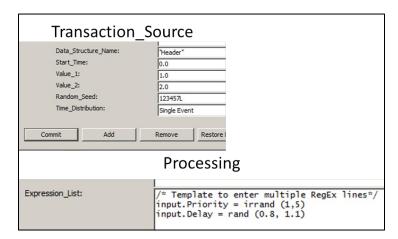

| 29 SO  | URCE                                               | 254 |

| 29.1   | GENERATING                                         | 254 |

| 30 RE  | SULT- ANALYSIS AND PLOTTING                        | 255 |

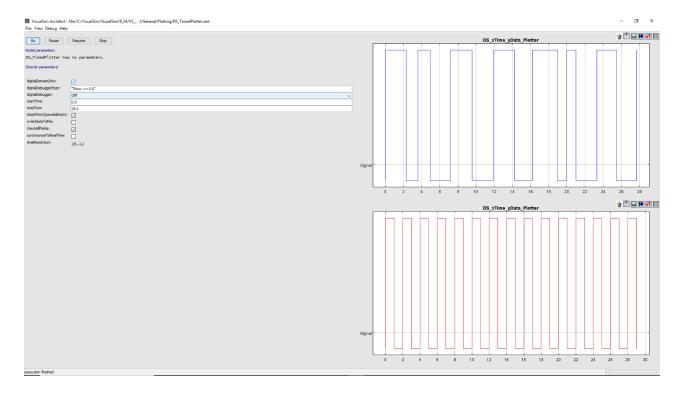

| 30.1   | .1 TimeDataPlotter Block Output                    | 257 |

| 31 RES | SOURCE                                             | 258 |

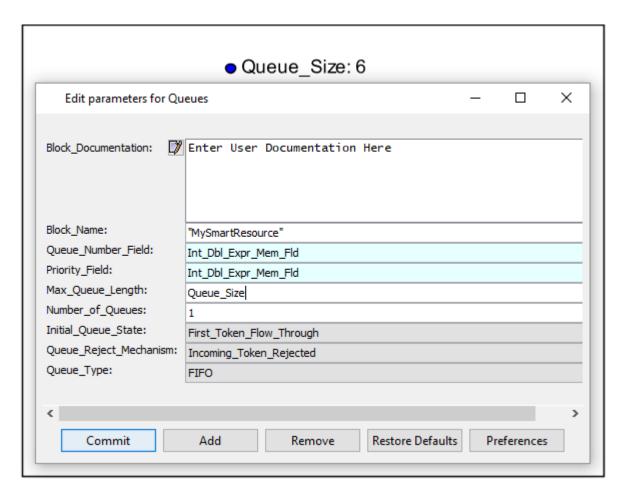

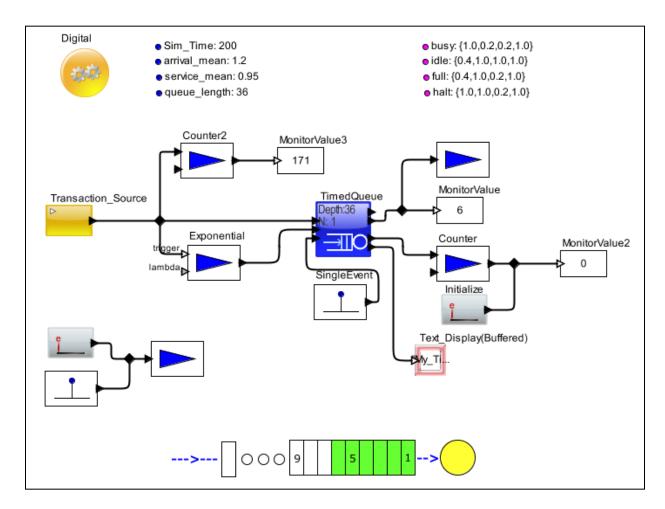

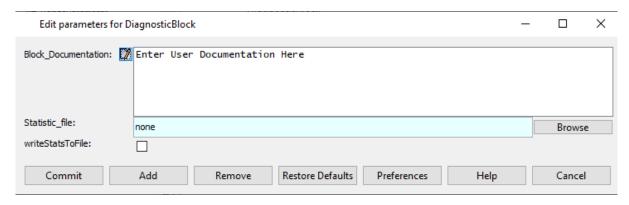

| 31.1   | QUEUES                                             | 259 |

| 31.2   | TIMED_QUEUES:                                      | 260 |

| 31.3   | Passive Resources:                                 | 261 |

| 31.4   | CHANNELS:                                          | 261 |

| 3  | 01.5        | SYSTEMRESOURCE                                                  | 202  |

|----|-------------|-----------------------------------------------------------------|------|

| 3  | 1.6         | KEY DIFFERENCE BETWEEN SYSTEMRESOURCE AND SYSTEMRESOURCE_EXTEND | 262  |

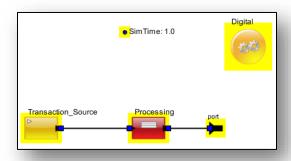

| 32 | PRO         | CESSING                                                         | .264 |

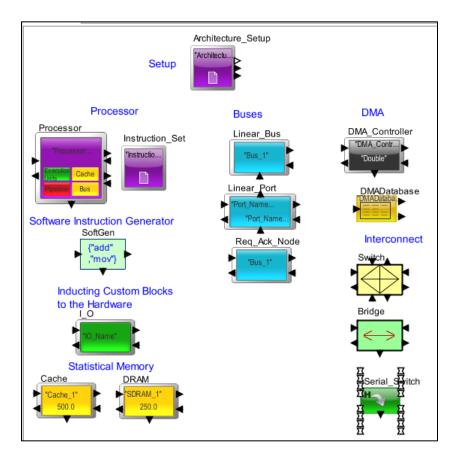

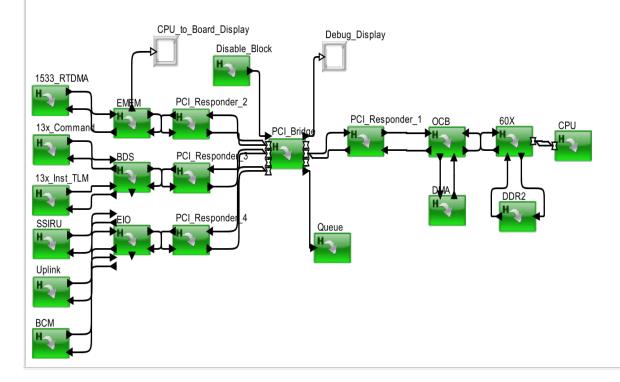

| 33 | HAR         | DWARE MODELING                                                  | .266 |

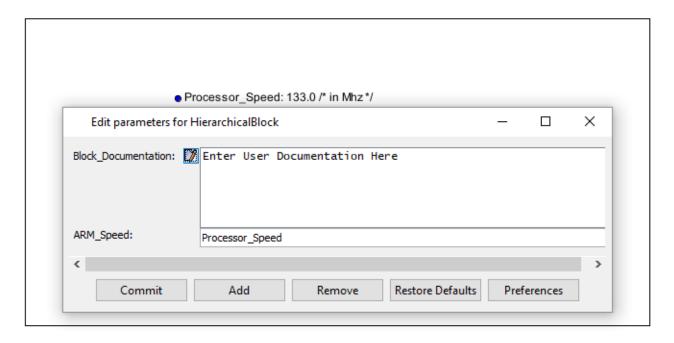

| 3  | 3.1         | Processor                                                       | 267  |

|    | 3.2         | SOFTWARE GENERATOR                                              |      |

|    | 3.3         | DRAM                                                            |      |

|    | 3.4         | INTEGRATED_CACHE                                                |      |

|    | 3.5         | LINEAR BUS                                                      |      |

|    | 3.6         | DMA                                                             |      |

|    | 3.7         | BRIDGE                                                          |      |

|    | 3.8         | SWITCH                                                          |      |

|    | 3.9         | SERIAL SWITCH                                                   |      |

|    |             | ES                                                              |      |

| ^  | 4.4         | AUD ADD                                                         | 070  |

|    | 4.1         | AHB AND APB                                                     |      |

|    | 4.2         | PCI AND PCIX                                                    |      |

|    | 4.3<br>4.4  | PCIE                                                            |      |

|    |             | CORECONNECT                                                     |      |

|    | 4.5         | SWITCHED ETHERNET                                               |      |

|    | 4.6<br>4.7  | SPACEWIRE                                                       |      |

|    |             | RAPIDIO                                                         |      |

|    | 4.8         |                                                                 |      |

|    | 4.9<br>4.10 | TIMETRIGGEREDETHERNET                                           |      |

|    | -           | AVIONICS FULL-DUPLEX SWITCHED ETHERNET                          |      |

|    | 4.11        | CAN/CAN-FD                                                      |      |

|    | 4.12        |                                                                 |      |

|    | 4.13        | TSN                                                             |      |

|    | 4.14        | PCI RAD                                                         |      |

| 35 | CYC         | LE-ACCURATE CACHE AND MEMORY                                    | .279 |

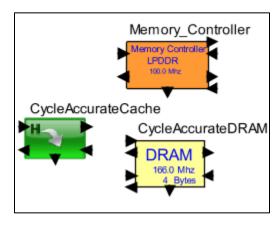

| 3  | 5.1         | CYCLE-ACCURATE CACHE                                            | 279  |

| 3  | 5.2         | CYCLE-ACCURATE MEMORY CONTROLLER                                | 279  |

| 35.3   | CYCLE-ACCURATE DRAM                                       | 279 |

|--------|-----------------------------------------------------------|-----|

| 36 PO  | WERTABLE                                                  | 282 |

| 37 SEI | ECTING THE RIGHT BLOCK FOR YOUR MODEL                     | 284 |

| 37.1   | Traffic Generation                                        | 284 |

| 37.2   | VARIABLES                                                 | 285 |

| 37.3   | PLOTTING                                                  | 286 |

| 37.4   | STATISTICS                                                | 289 |

| 37.5   | Power Statistics                                          | 289 |

| 37.6   | RESOURCES AND HARDWARE                                    | 290 |

| 37.7   | UTILITIES AND FUNCTIONS                                   | 293 |

| 38 AC  | CELERATING MODEL SIMULATION PERFORMANCE                   | 295 |

| 39 ERI | ROR MESSAGES                                              | 297 |

| 40 MO  | DEL-LEVEL DEBUGGING                                       | 298 |

| 40.1   | MODEL ANIMATION                                           | 299 |

| 40.2   | PROBES, DISPLAY AND STATISTICS                            | 299 |

| 40.3   | LISTEN TO SIMULATOR                                       | 300 |

| 40.4   | LISTEN TO PORT                                            | 300 |

| 40.5   | LISTEN TO BLOCK                                           | 301 |

| 40.6   | SCRIPT PROFILER FOR THE SCRIPT BLOCK AND SMART CONTROLLER | 301 |

| 40.7   | LISTEN TO FILE FOR SCRIPT BLOCK AND SMART CONTROLLER      | 302 |

| 40.8   | DEBUGGING VARIABLE                                        | 302 |

| 40.9   | Debugging a New Model                                     | 303 |

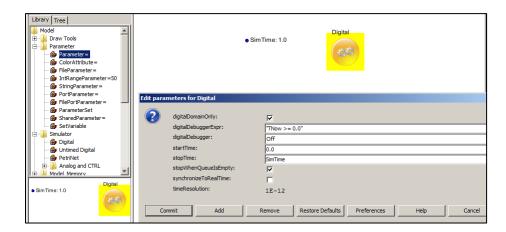

| 40.10  | DIGITAL DEBUGGING                                         | 304 |

| 40.11  | DEBUGGING SCRIPTS                                         | 305 |

| 40.12  | SETTING BREAKPOINTS                                       | 306 |

| 40.1   | 2.1 Set Breakpoints context menu choice                   | 306 |

| 40.13  | Pause and Resume function with Debugging facility         | 307 |

| 40.1   | 3.1 How to Use Pause and Resume Function                  | 307 |

| 40.1   | 3.2 Steps:                                                | 307 |

| 40.14  | TESTING THE RTL                                           | 308 |

| 40 15  | HOW TO DEBUG- USING THE METHODOLOGY PROVIDED              | 308 |

| 40.15   | 5.1 INTRODUCTION                                                         | 308        |

|---------|--------------------------------------------------------------------------|------------|

| 40.15   | 5.2 Animate                                                              | 309        |

| 40.15   | 5.3 Listen To Simulator                                                  | 309        |

| 40.15   | 5.4 Listen To Port                                                       | 310        |

| 40.15   | 5.5 Listen To Block                                                      | 310        |

| 40.15   | 5.6 Tracer                                                               | 310        |

| 40.15   | 5.7 Difficulties in debugging any system and how it is different from de | ebugging a |

| regul   | ar piece Java or C/C++ code                                              | 311        |

| 40.15   | 5.8 Sequence for debugging                                               | 311        |

| 41 SOF  | TWARE ESTIMATION AND MODELING                                            | 313        |

| 41.1    | Approaches                                                               | 313        |

| 41.2    | Abstract approach                                                        |            |

| 41.3    | CYCLE-ACCURATE APPROACH                                                  | 315        |

| 41.4    | ADDING FUNCTIONALITY TO THE TIMING ACCURATE MODEL                        | 316        |

| 41.5    | USING QEMU VIRTUAL ENVIRONMENT FOR SYSTEM SIZING                         | 316        |

| 42 C C  | ODE SOFTWARE ANNOTATION                                                  | 319        |

| 42.1    | DESCRIPTION                                                              | 319        |

| 42.2    | STEP-BY-STEP                                                             | 320        |

| 42.3    | EXAMPLE OF GENERATED TASK SENT TO PROCESSOR                              | 321        |

| 43 CON  | NCEPT OF TIME                                                            | 337        |

| 43.1    | Introduction                                                             | 337        |

| 43.2    | TIME RESOLUTION                                                          | 337        |

| 43.3    | SIMULATION TIME                                                          | 338        |

| 43.4    | RELATIVE VS CLOCK TIME                                                   | 338        |

| 43.5    | COMPUTING TIME                                                           | 338        |

| 43.6    | CLOCK SYNCHRONIZATION                                                    | 339        |

| 43.7    | MODEL EVENT                                                              | 339        |

| 44 INTI | RODUCTION TO FINITE STATE MACHINE                                        | 341        |

| 44.1    | FINITE STATE MACHINE                                                     | 341        |

| 44.1.   | 1 FSM-Controller                                                         | 341        |

| 44 1    | 2 Guard Expressions                                                      | 342        |

| 44.1   | .3 Actions                                                                        | 342   |

|--------|-----------------------------------------------------------------------------------|-------|

| 44.2   | EXECUTION                                                                         | 342   |

| 44.3   | FINITESTATEMACHINE                                                                | 343   |

| 45 EXF | PLORER, EXPORT TO HTML AND HTML PAGE GENERATION                                   | 344   |

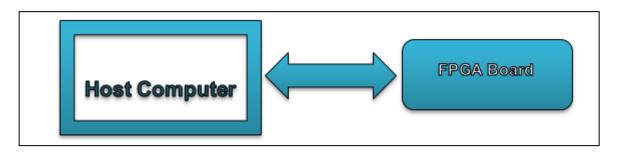

| 46 VIS | UALSIM® INTERFACE WITH FPGA                                                       | 346   |

| 46.1   | VISUALSIM FPGA INTERFACE APPLICATIONS                                             | 346   |

| 46.2   | HARDWARE AND SOFTWARE REQUIREMENTS                                                | 347   |

| 46.3   | VISUALSIM FPGA INTERFACE KIT                                                      | 347   |

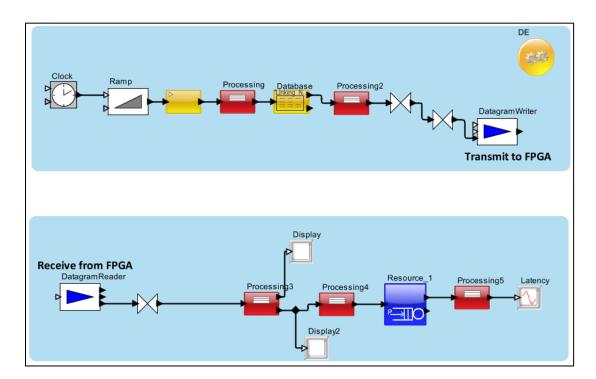

| 46.4   | How Interface Works                                                               | 347   |

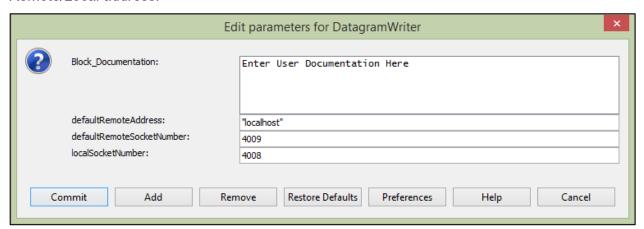

| 46.4   | .1 Procedure to Run Example                                                       | 348   |

| 46.5   | CONFIGURING FPGA AND SOURCE FILES                                                 | 350   |

| 46.6   | Possible Errors                                                                   | 353   |

| 46.7   | Appendix                                                                          | 354   |

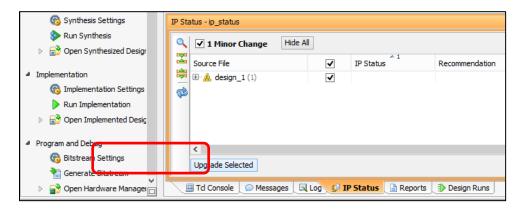

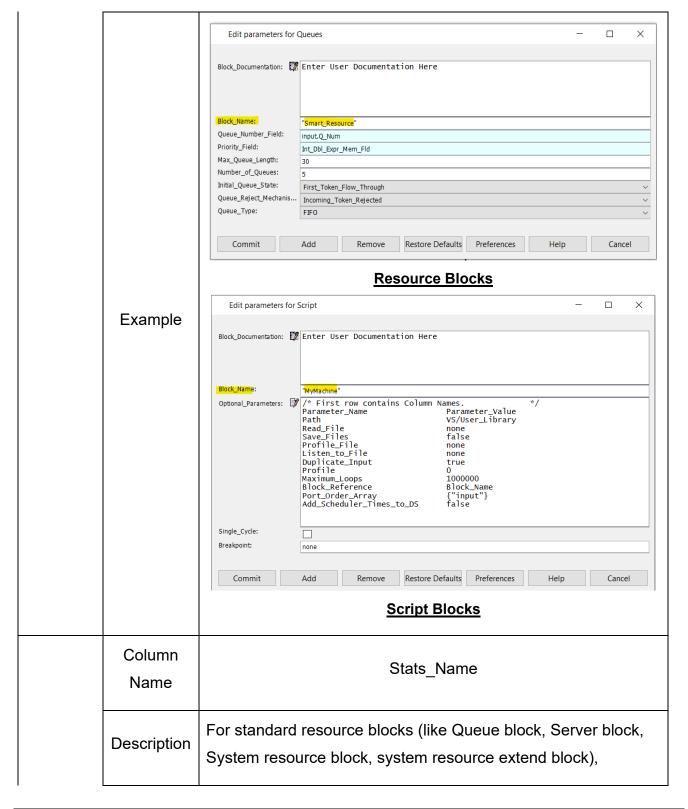

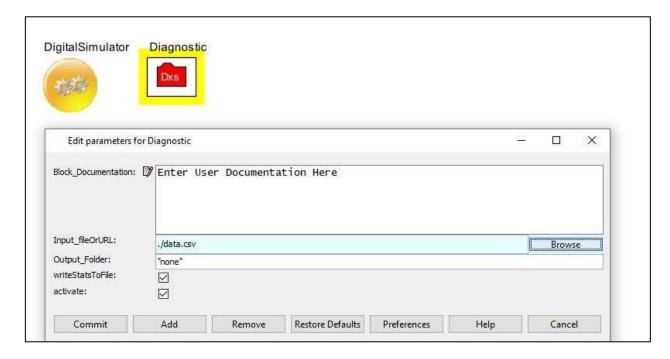

| 47 DIA | GNOSTIC ENGINE                                                                    | 356   |

| 47.1   | FEATURES OF DIAGNOSTIC BLOCK:                                                     | 356   |

| 47.2   | FILE REQUIRED FOR GENERATING STATISTICS:                                          | 356   |

| 47.3   | OUTPUT FILE                                                                       | 383   |

| 47.4   | VISUALSIM BLOCKS SUPPORTED                                                        | 385   |

| 47.5   | VIRTUAL CONNECTION IN DIAGNOSTIC BLOCK                                            | 385   |

| 48 QEI | MU GUIDE                                                                          | 386   |

| 48.1   | STEPS TO INSTALL QEMU ON UBUNTU                                                   | 386   |

| 48.2   | DOWNLOAD BENCHMARK TO RUN THE PROGRAM                                             | 387   |

| 48.3   | STEPS TO COMPILE AND RUN C PROGRAM FOR X86 AND ARM                                | 387   |

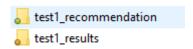

| 49 VIS | UALSIM GEM5-ARM INTEGRATION                                                       | 395   |

| 49.1   | INSTALLATION STEPS FOR UBUNTU OS                                                  | 395   |

| Assum  | PTION: THE USER HAS INSTALLED JAVA VERSION 14 OR LATER AND VISUALSIM ARCHI<br>395 | ГЕСТ. |

| 49.2   | Installation steps for CentOS 8.3                                                 | 395   |

| Assum  | PTION: THE USER HAS INSTALLED JAVA VERSION 14 OR LATER AND VISUALSIM ARCHI<br>395 | ГЕСТ. |

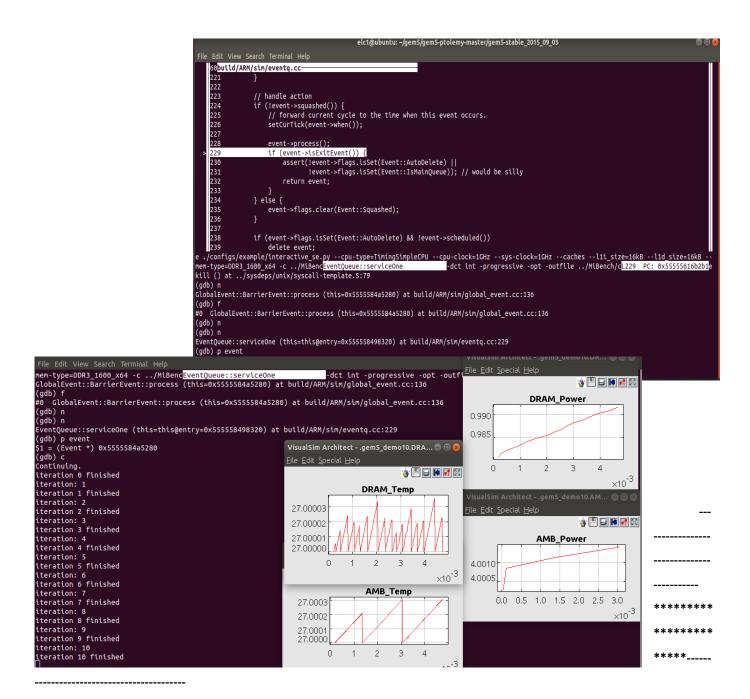

| 49.3   | Run the Gem5 with Visualsim                                                       | 396   |

| 49.4      | TRACE GENERATION FROM GEM5:                                         | 397        |

|-----------|---------------------------------------------------------------------|------------|

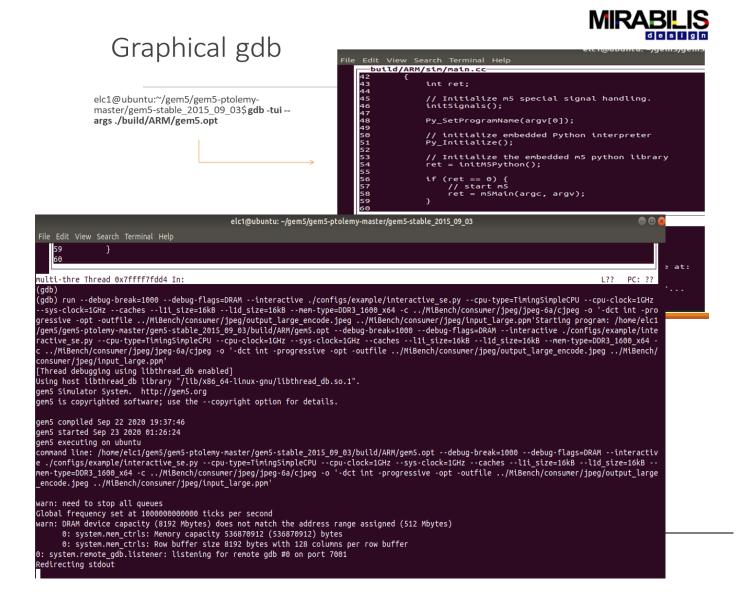

| 49.5      | DEBUG GEM5 USING GDB:                                               | 397        |

| 49.6      | DEBUG GEM5 USING GRAPHICAL GDB:                                     | 398        |

| 49.7      | RUNNING THE GEM5 IN SYSTEM CALL EMULATION (SE) MODE                 | 401        |

| 49.8      | RUN THE GEM5 (SE MODE) IN MULTI-CORE                                | 402        |

| 49.9      | RUNNING THE GEM5 IN FULL SYSTEM (FS) MODE                           | 403        |

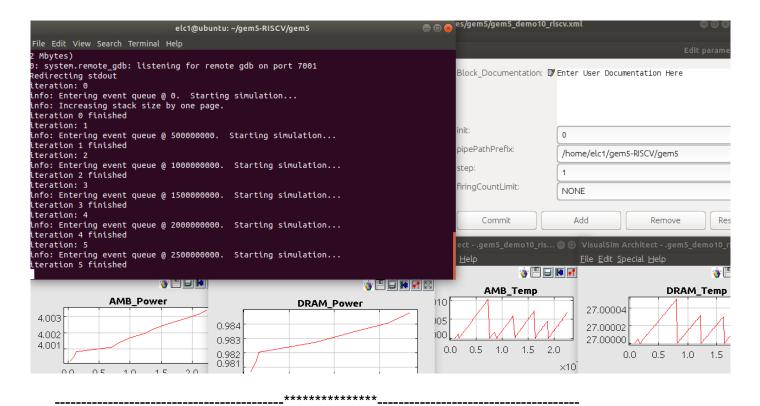

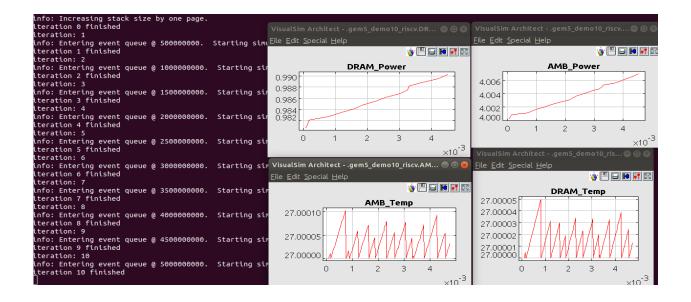

| 50 GEM    | 5 WITH RISCV                                                        | 409        |

| 50.1      | FOR UBUNTU 18.04 INSTALLATION STEPS                                 | 409        |

| 50.2      | RUN THE GEM5 <-> VISUALSIM (NORMAL RUN WITHOUT DEBUGGER)            | 409        |

| 50.3      | RUN WITH DEBUGGER -COMMAND LINE:                                    | 411        |

| 50.4      | RUN WITH DEBUGGER - GRAPHICAL GDB:                                  | 413        |

| 50.5      | RUNNING THE GEM5 IN SYSTEM CALL EMULATION (SE) MODE                 | 415        |

| 50.6      | RUNNING THE GEM5 (SE MODE) IN MULTI-CORE                            | 416        |

| 50.7      | RUNNING THE GEM5 IN FULL SYSTEM (FS) MODE                           | 417        |

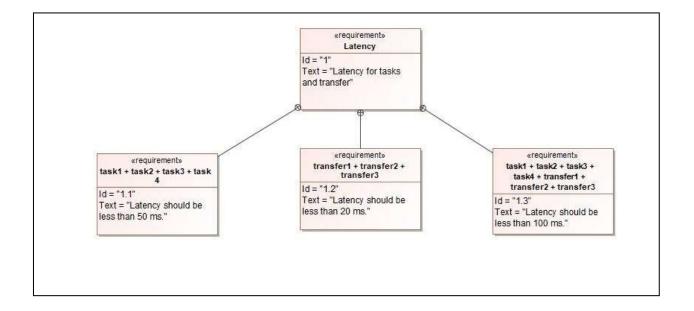

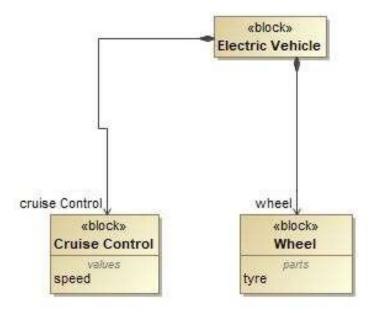

| 51 SYSI   | ML TO VISUALSIM                                                     | 418        |

| 51.1      | Pre-Requisite:                                                      | 419        |

| 51.2      | FEATURES SUPPORTED BY XML CONVERTER:                                | 419        |

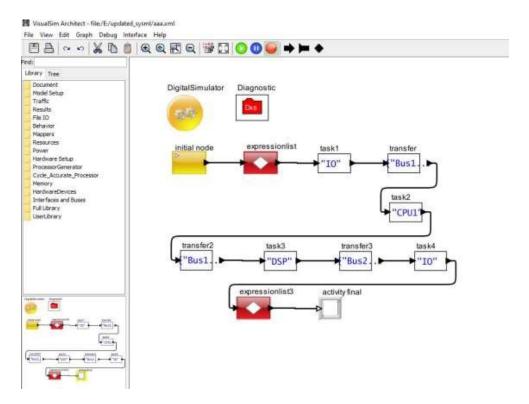

| 51.3      | ACTIVITY AND REQUIREMENT DIAGRAM                                    | 421        |

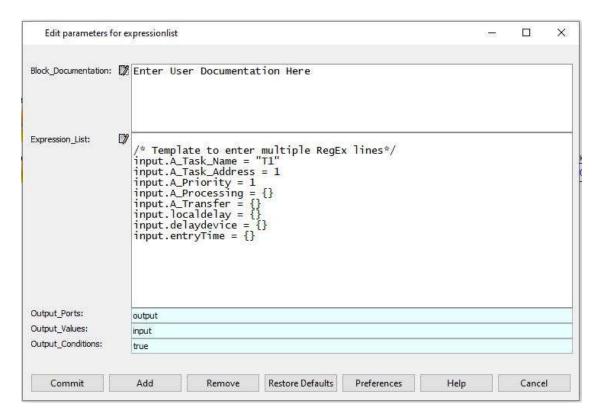

| 51.3.1    | Steps to import Activity Diagram in VisualSim                       | 421        |

| USING TH  | HIS METHODOLOGY, YOU CAN EVALUATE THE PERFORMANCE OF ANY $SYSML$ AC | CTIVITY IN |

| VISUALS   | IM                                                                  | 429        |

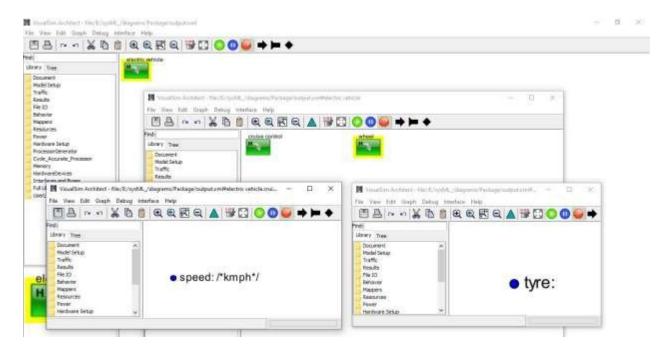

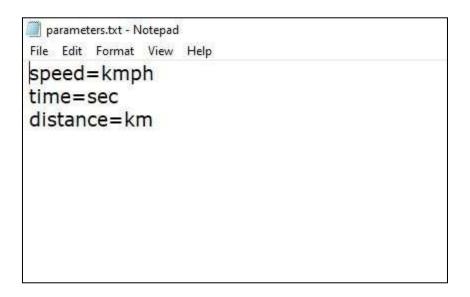

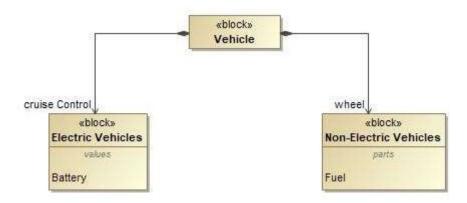

| 51.4      | PACKAGE DIAGRAM                                                     | 429        |

| 51.4.1    | Steps to import Package Diagram in VisualSim                        | 429        |

| 51.5      | BLOCK DIAGRAM                                                       | 434        |

| 51.5.1    | Steps to import Block Diagram in VisualSim                          | 434        |

|           | TABLE OF FIGURES                                                    |            |

| FIGURE 1. | VISUALSIM PLOT APPLICATION WINDOW                                   | 40         |

| FIGURE 2. | APPLETVIEWER                                                        | 43         |

| FIGURE 3. | ZOOM IN                                                             | 43         |

| FIGURE 4. | PLOT                                                                | 45         |

| EICUDE 5  | SIMILI ATION COCKRIT                                                | 66         |

| FIGURE 6.  | BLOCK EXECUTION SEMANTICS                              | 70  |

|------------|--------------------------------------------------------|-----|

| FIGURE 7.  | BLOCK ATTRIBUTES                                       | 70  |

| FIGURE 8.  | BLOCK CONTEXT MENU                                     | 71  |

| FIGURE 9.  | PORTS THAT CANNOT BE EDITED.                           | 71  |

| FIGURE 10. | SET PORTS TO BLOCK                                     | 78  |

| FIGURE 11. | LINKING PARAMETER                                      | 79  |

| FIGURE 12. | HIERARCHICAL BLOCK -> OPEN BLOCK                       | 82  |

| FIGURE 13. | ADDING BLOCKS TO A HIERARCHICAL BLOCK                  | 83  |

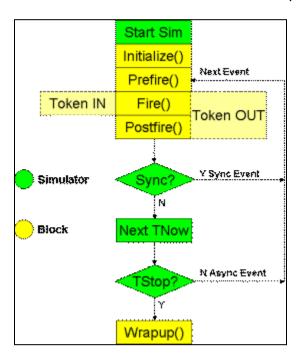

| FIGURE 14. | MODEL EXECUTION SEMANTICS                              | 85  |

| FIGURE 15. | MODEL EXECUTION FLOWCHART                              | 85  |

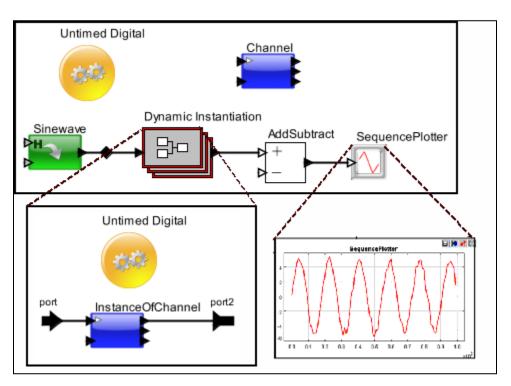

| FIGURE 16. | A MODEL USING THE DYNAMIC INSTANTIATION BLOCK          | 87  |

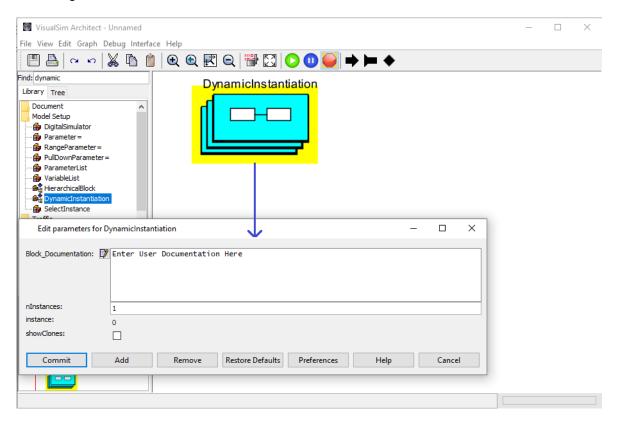

| FIGURE 17. | CONFIGURE PARAMETERS FOR DYNAMIC INSTANTIATION         | 88  |

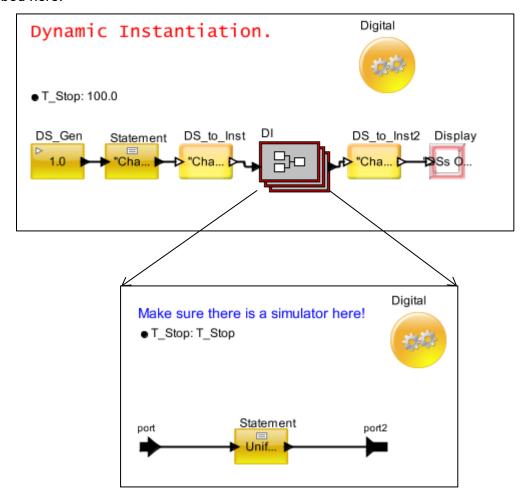

| FIGURE 18. | DYNAMIC INSTANTIATION EXAMPLE IN VISUALSIM             | 90  |

| FIGURE 19. | LIBRARY FOLDER ORGANIZATION                            | 92  |

| FIGURE 20. | BLOCKS IN DOCUMENT/ MODEL / MODELSETUP LIBRARY FOLDERS | 93  |

| FIGURE 21. | BLOCKS IN SOURCE LIBRARY                               | 94  |

| FIGURE 22. | BLOCKS IN RESULT LIBRARY                               | 95  |

| FIGURE 23. | CONTROL FLOW BLOCKS                                    | 96  |

| FIGURE 24. | Mappers                                                | 97  |

| FIGURE 25. | BLOCKS IN RESOURCE LIBRARY                             | 98  |

| FIGURE 26. | Power                                                  | 99  |

| FIGURE 27. | HARDWARE SETUP                                         | 100 |

| FIGURE 28. | Processor Generator                                    | 101 |

| FIGURE 29. | MEMORY                                                 | 101 |

| FIGURE 30. | BLOCKS IN HARDWARE DEVICES                             | 102 |

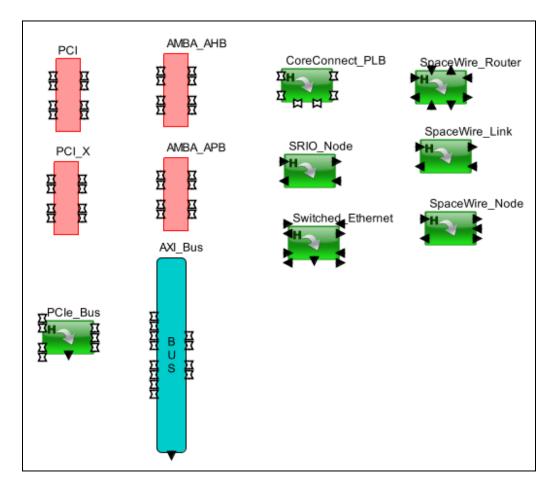

| FIGURE 31. | INTERFACES AND BUSES                                   | 103 |

| FIGURE 32. | Interface Blocks                                       | 104 |

| FIGURE 33. | MATH OPERATIONS LISTING                                | 104 |

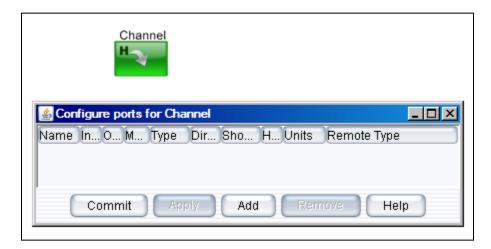

| FIGURE 34. | Configure Ports                                        | 108 |

| FIGURE 35. | HIERARCHICAL MODEL TO CREATE A CLASS                   | 109 |

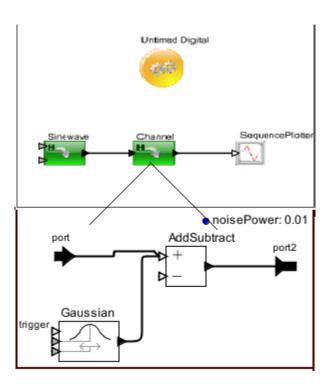

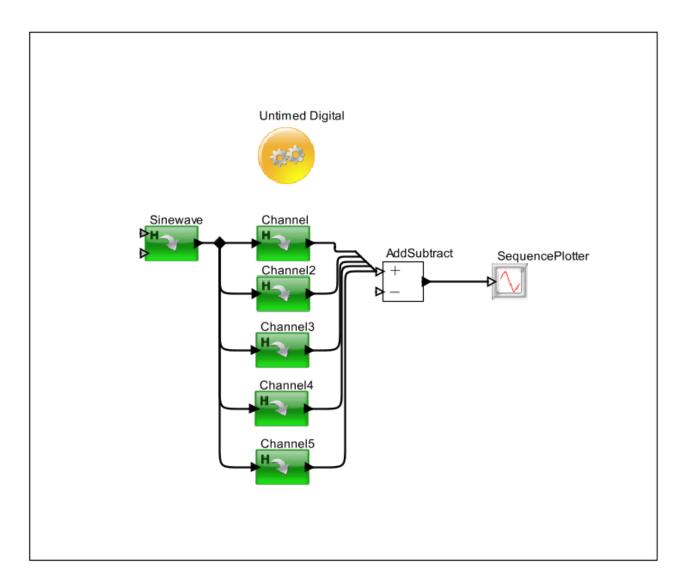

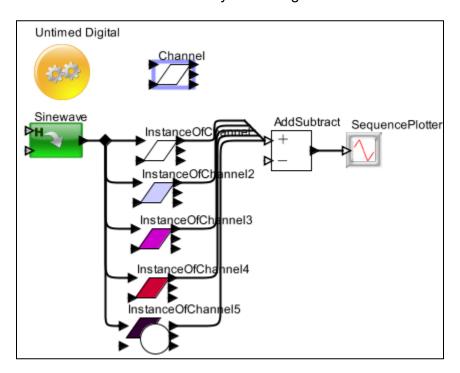

| FIGURE 36. | A POOR DESIGN OF A DIVERSITY COMMUNICATION SYSTEM      | 110 |

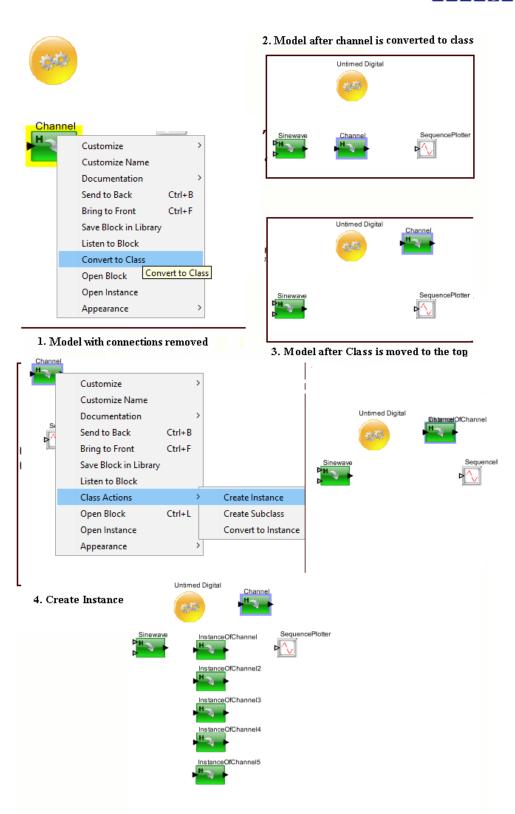

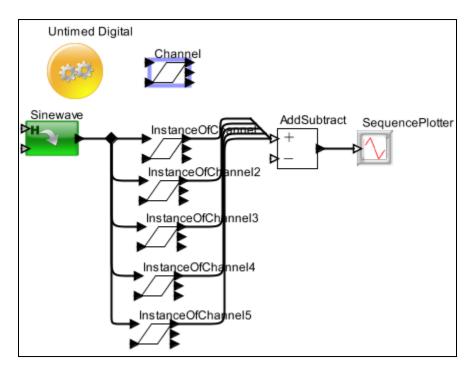

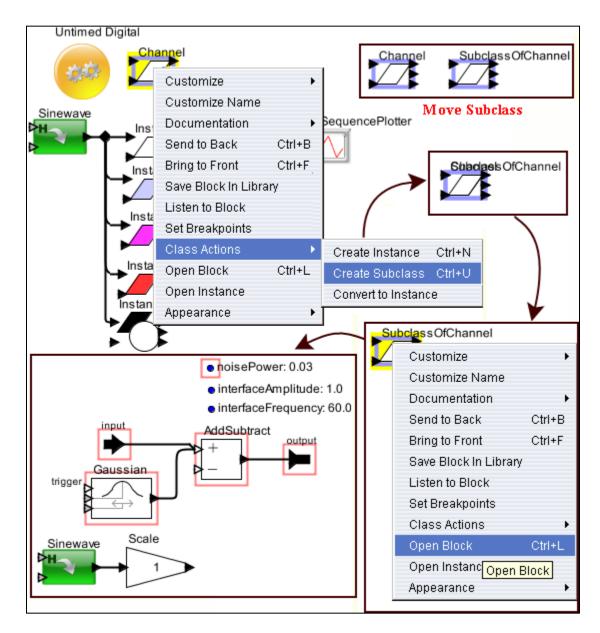

| FIGURE 37. | CREATING AND USING A CHANNEL CLASS                     | 113 |

| FIGURE 38  | THE ICON CHANGED FOR THE CLASS                         | 113 |

| FIGURE 39. | MODEL WITH THE ICONS OF THE INSTANCE                          | 114 |

|------------|---------------------------------------------------------------|-----|

| FIGURE 40. | THE MODEL WITH A SUBCLASS OF THE CHANNEL WITH NO OVERRIDES    | 116 |

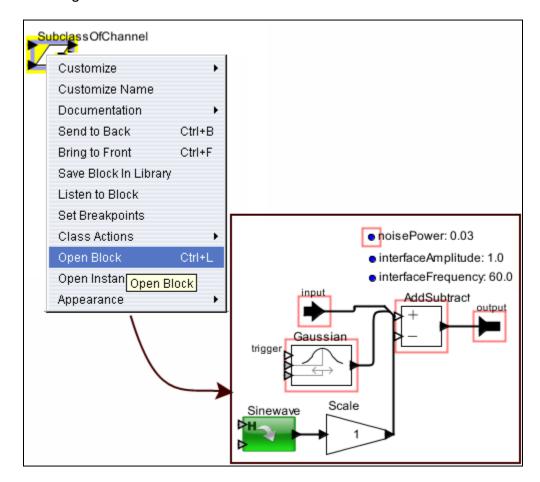

| FIGURE 41. | THE SUBCLASS WITH OVERRIDES THAT ADD SINUSOIDAL INTERFERENCES | 117 |

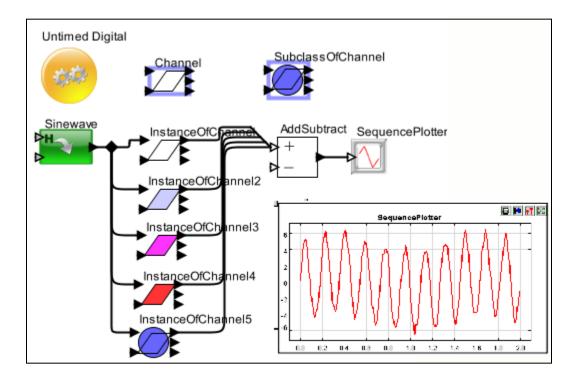

| FIGURE 42. | A MODEL USING THE SUBCLASS FORM AND A PLOT OF THE EXECUTION   | 118 |

| FIGURE 43. | CREATE A BLOCK DIAGRAM                                        | 123 |

| FIGURE 44. | BLOCK ATTRIBUTES                                              | 123 |

| FIGURE 45. | Making the Connection and Select+All                          | 123 |

| FIGURE 46. | CREATE A CLASS                                                | 124 |

| FIGURE 47. | INSTANTIATE CLASS TO IMPORT A CLASS                           | 125 |

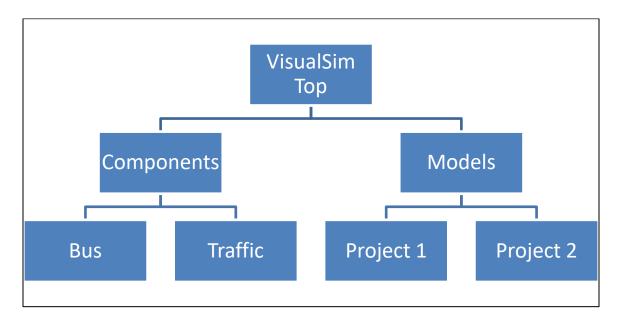

| FIGURE 48. | VISUALSIM RECOMMENDED DIRECTORY STRUCTURE                     | 128 |

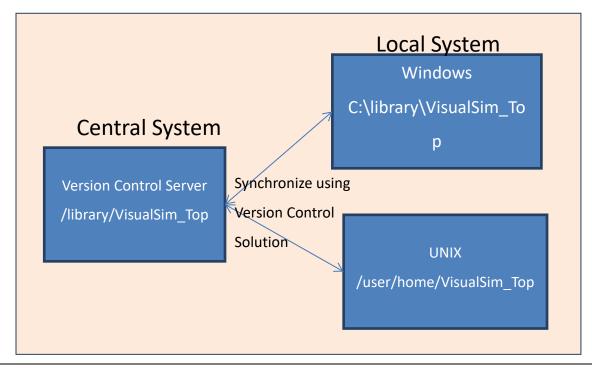

| FIGURE 49. | LIBRARY INTEGRATION BETWEEN CENTRAL AND LOCAL SYSTEM          | 129 |

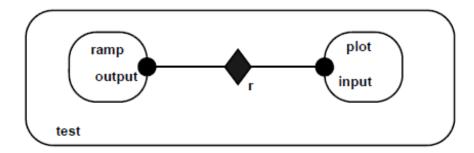

| FIGURE 50. | SIMPLE EXAMPLE                                                | 131 |

| FIGURE 51. | SIMPLE EXAMPLE OF A VISUALSIM MODEL EXECUTION CONTROL WINDOW  | 131 |

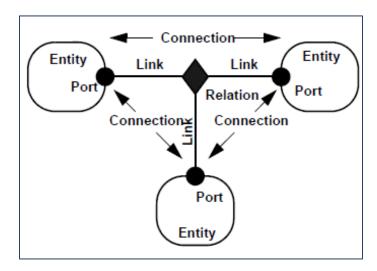

| FIGURE 52. | VISUAL NOTATION AND TERMINOLOGY                               | 132 |

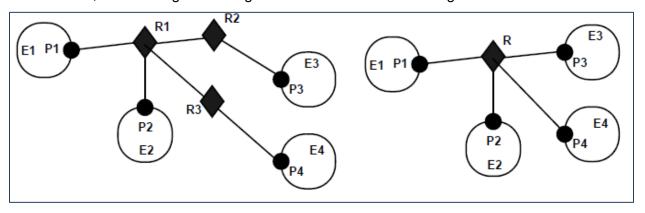

| FIGURE 53. | RELATIONSHIP GROUPS                                           | 133 |

| FIGURE 54. | EXAMPLE TOPOLOGY.                                             | 143 |

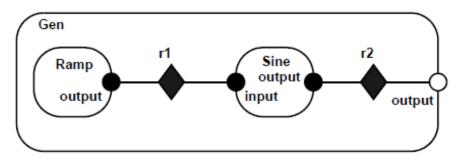

| FIGURE 55. | SINE WAVE GENERATOR TOPOLOGY.                                 | 147 |

| FIGURE 56. | VERTEX EXAMPLE                                                | 150 |

| FIGURE 57. | EXAMPLE OF A FUNCTION BEING PASSED FROM ONE ACTOR TO ANOTHER  | 185 |

| FIGURE 58. | ELABORATE USE                                                 | 185 |

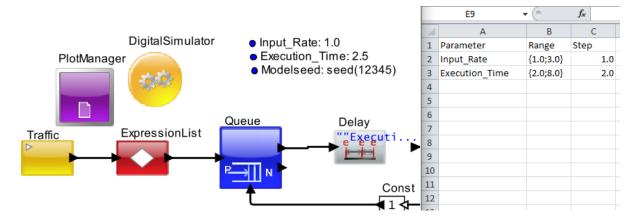

| FIGURE 59. | USING PARAMETERS IN EXPRESSIONS                               | 211 |

| FIGURE 60. | USING PARAMETERS TO SET BLOCK ATTRIBUTES                      | 212 |

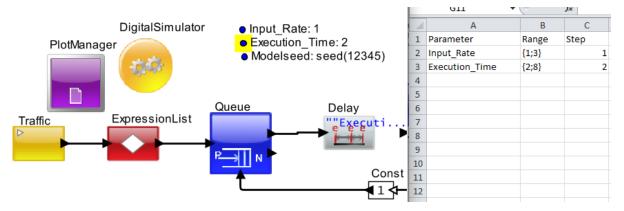

| FIGURE 61. | LINKING PARAMETERS                                            | 214 |

| FIGURE 62. | USING PARAMETERS TO SET THE ICON COLOR                        | 216 |

| FIGURE 63. | CONFIGURE PORTS FOR THE BLOCK                                 | 217 |

| FIGURE 64. | PORTS THAT CANNOT BE EDITED                                   | 218 |

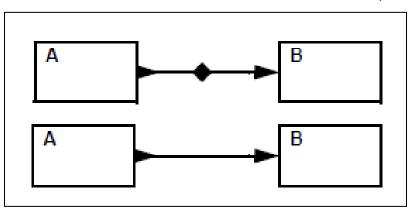

| FIGURE 65. | BLOCK-TO-BLOCK CONNECTIONS                                    | 223 |

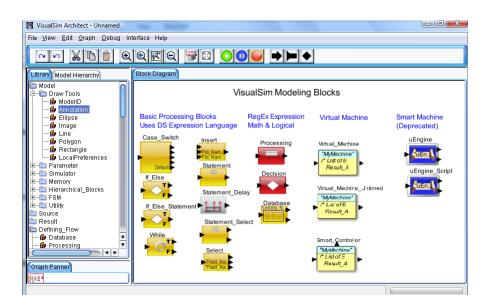

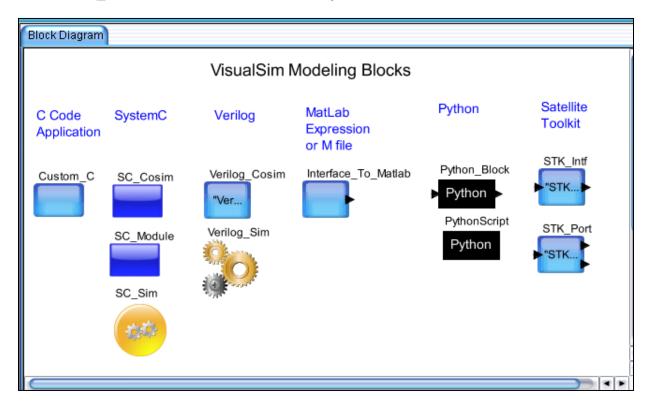

| FIGURE 66. | VISUALSIM MODELING LANGUAGES                                  | 234 |

| FIGURE 67. | LIST OF APPLICATION INTERFACE BLOCKS                          | 236 |

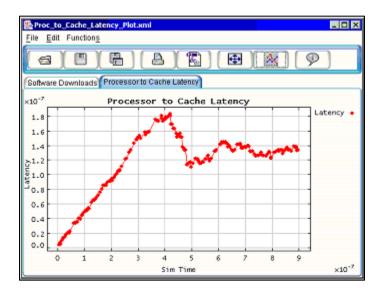

| FIGURE 68. | POST PROCESSING LATENCY                                       | 256 |

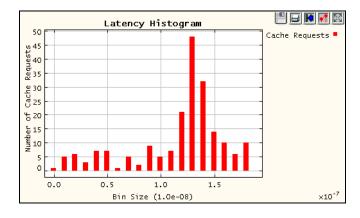

| FIGURE 69. | POST PROCESSING HISTOGRAM                                     | 256 |

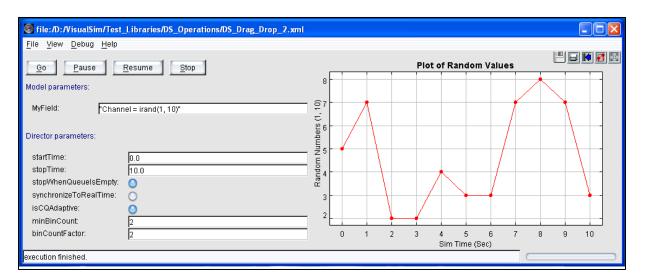

| FIGURE 70. | MODEL PLOT                                                    | 257 |

| FIGURE 71  | HADDWADE MODELING LIBRADY                                     | 266 |

| FIGURE 72. | LIST OF HARDWARE BUSES                           | 270 |

|------------|--------------------------------------------------|-----|

| FIGURE 73. | CYCLE-ACCURATE CACHE AND MEMORY MODELS           | 279 |

| FIGURE 74. | MODEL ANIMATION                                  | 299 |

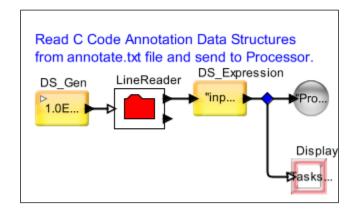

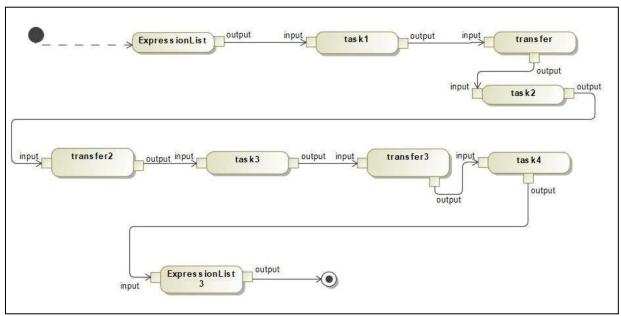

| FIGURE 75. | ANNOTATION WITH LINEREADER PLUS PROCESSING BLOCK | 327 |

| FIGURE 76. | FINITESTATEMACHINE ILLUSTRATION                  | 343 |

| FIGURE 77. | EXPORT TO WEB DIALOG WINDOW                      | 344 |

| FIGURE 78. | VISUALSIM INTERFACE WITH FPGA                    | 346 |

| FIGURE 79. | VISUALSIM MODEL                                  | 349 |

| FIGURE 80. | CONFIGURING DATAGRAM WRITER BLOCK                | 349 |

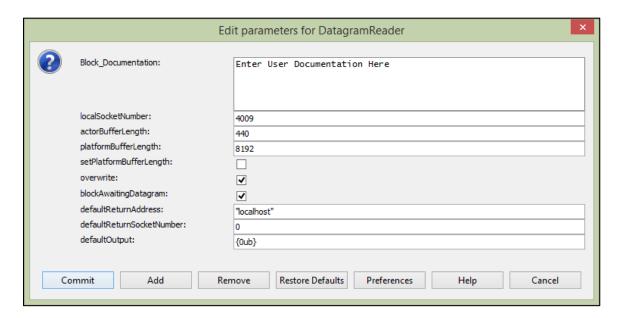

| FIGURE 81. | CONFIGURING DATAGRAM READER                      | 350 |

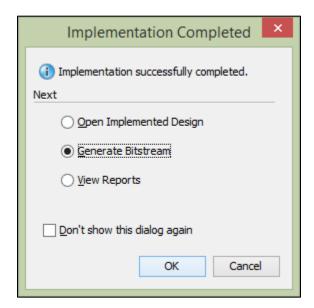

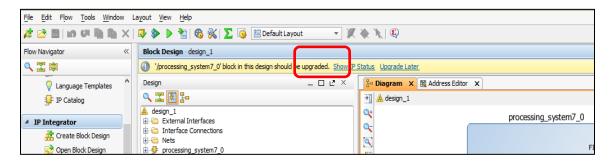

| FIGURE 82. | GENERATE BITSTREAM                               | 351 |

| FIGURE 83. | GENERATE BITSTREAM                               | 351 |

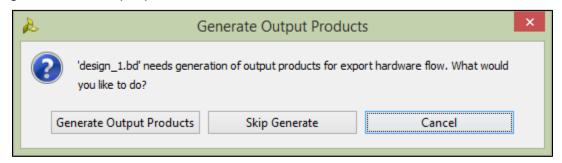

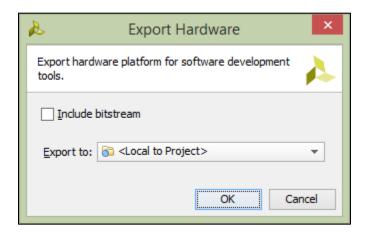

| FIGURE 84. | EXPORT HARDWARE                                  | 352 |

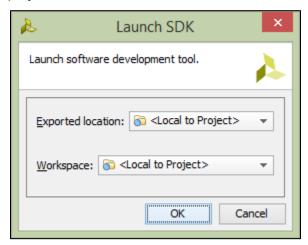

| FIGURE 85. | Launch SDK                                       | 352 |

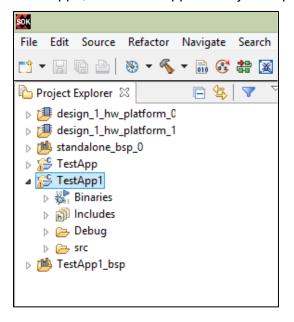

| FIGURE 86. | PROJECT EXPLORER                                 | 353 |

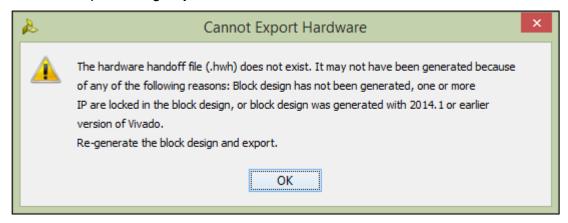

| FIGURE 87. | CANNOT EXPORT HARDWARE                           | 354 |

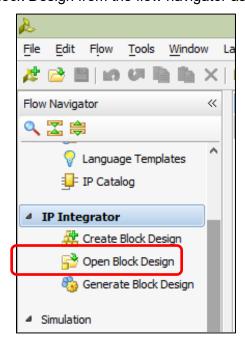

| FIGURE 88. | OPEN BLOCK DESIGN                                | 355 |

| FIGURE 89. | Show IP Status                                   | 355 |

| FIGURE 90. | UPDATE SELECTED                                  | 355 |

| FIGURE 91. | RECOMMENDATION ENGINE BLOCK                      | 356 |

# 1 Scope and Purpose of the Document

## 1.1 Introduction

Mirabilis Design provides systems engineering solutions for performance analysis, power estimation, and architecture exploration of electronics and real-time software. Mirabilis' product **VisualSim** is used for performance, functional, and power exploration of network of systems, large systems, sub-systems, components (IC, SoC, FPGA, and boards) and real-time software. VisualSim models are constructed in a graphical block diagram editor using a parameterized modeling blocks library.

## 1.2 Scope

This document provides the information required to enable the reader to construct system models, execute simulations, and analyze the results with an intent to optimize the specification. This document explains the basic components in this framework, the simulator, modeling language, and provides an overview of the libraries.

The intended audience for this document is an engineer or researcher who wishes to construct models in VisualSim, debug these models, and conduct analysis. The goal of the exploration is to architect the right product, that is one which minimizes product failures and has not been over or under designed.

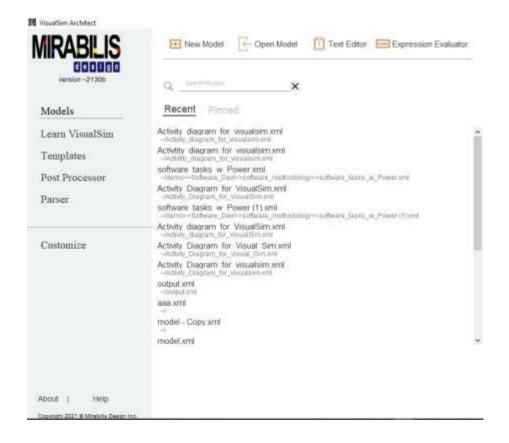

# 2 Starting VisualSim

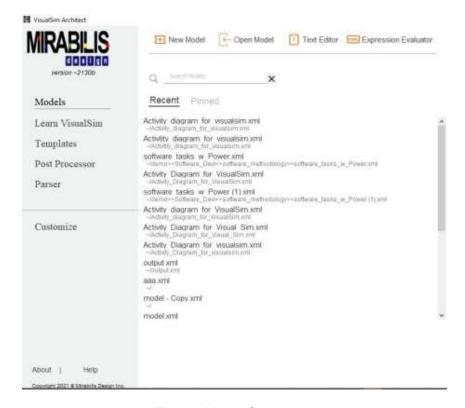

## 2.1 Running VisualSim Architect

To start Architect, do one of the following:

- ⇒ Double-click Architect icon on the Window or in the Application Menu.

- ⇒ Double-click VisualSim.bat (WINDOWS) or VisualSim.sh (UNIX) in the VisualSim directory viewer.

- ⇒ From a Command-line or system-prompt or shell window, go to the VisualSim install and type VisualSim.bat (Windows) and VisualSim.sh (UNIX).

To start the Post Processor, do the following:

- ⇒ Double-click the Post Processor icon in the Window or in the Application Menu.

- ⇒ Double-click PostProcessor.bat (WINDOWS) or PostProcessor.sh (UNIX) in the Post Processor directory.

- ⇒ From a Command-line, system-prompt or shell window, go to the Post Processor install and type PostProcessor.bat (Windows) or PostProcessor.sh (UNIX).

# 2.3 Running VisualSim Explorer

To start VisualSim Explorer, do the following:

- 1. The user needs to start the License Server located in the Web Server.

- 2. To start the License Manager, locate the install directory and navigate to VS\_LM.

- 3. From a Command-line, system-prompt or shell window, type StartServer.bat (Windows) or StartServer.sh (UNIX).

- 4. The user can access html pages on this system by opening the page in their respective browser.

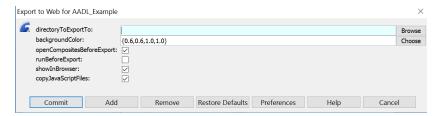

- The Interfaces > Export to Web can be used to export the model for use in the browser.

# 3 VisualSim Products, Editors, and Tools

## 3.1 Block Diagram Editor

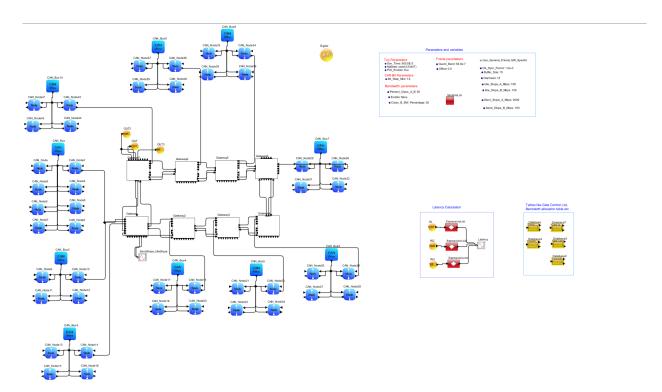

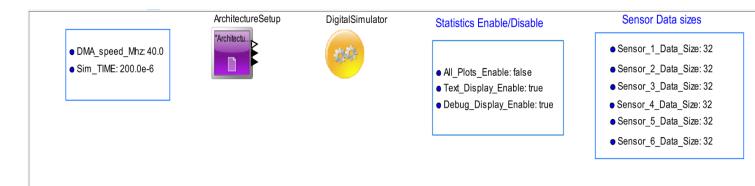

The Block Diagram Editor (BDE) is the main editor in the VisualSim Architect environment. Users construct, debug, validate, and optimize the models of their system in this environment. Simulations to validate the model and get early feedback on the architecture are conducted from the Editor. After the model is stable and simulations are restricted to parameter changes, the Batch Mode can be used for large scale system analysis.

In the BDE, select blocks from the core libraries, place them on the BDE canvas, and then connect the blocks to represent the functions of the system. Group the various functions of the system to form a hierarchical model representing a sub system. Make use of hierarchy and aggregation to manage the complexity of large systems. Include adjustable parameters in any model so as to easily modify the system performance as per the requirement. Users can alter random number seeds to investigate system stability through analysis of variance. Prior to simulation, assign each parameter a value to execute a simulation over a range of conditions. Moreover, easily incorporate measured characteristics of the system, such as traffic traces, into VisualSim models.

#### 3.1.1 Menu Commands

| Menu | Sub Menu  | Explanation                                                                                                                   | Shortcut |

|------|-----------|-------------------------------------------------------------------------------------------------------------------------------|----------|

|      | Open File | Select and open an existing model, text or html file on a local or networked disk.                                            | Ctrl+O   |

| File | Open URL  | Select and open an existing model, text or html file using the URL address. The file can be located anywhere on the Internet. |          |

| Menu | Sub Menu                | Explanation                                                                                                                                                  | Shortcut |

|------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | New                     | Open a new Block Diagram Editor (BDE), Icon Editor, FSM-Controller, FiniteStateMachine, Text Editor, Expression Evaluator or Tcl Evaluator.                  |          |

|      | Save                    | Save the active file with its current file name, location, and format.                                                                                       | Ctrl+S   |

|      | Save as                 | Save by opening a window to change the file name, location or format.                                                                                        |          |

|      | Print                   | Print the active file. User can change the print options.                                                                                                    | Ctrl+P   |

|      | Import                  | Import an existing file.                                                                                                                                     |          |

|      | Export                  | Export to png, gif, Web Page (Different from the dynamic Export to HTML), and Save in Library (Saves the entire model content as a library in User_Library). |          |

|      | Recent Files            | View a list of the last 10 files that are saved for you to easily select.                                                                                    |          |

|      | Close                   | Close the active window.                                                                                                                                     | Ctrl+W   |

|      | Exit                    | Close the application.                                                                                                                                       |          |

| View | Block Diagram<br>Editor | Switch from the existing window to Block Diagram Editor window. This feature is disabled.                                                                    |          |

| Menu | Sub Menu              | Explanation                                                                                                                               | Shortcut                       |

|------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

|      | Simulation<br>Cockpit | View Simulation Cockpit of the model to modify the parameters and to run the model. This feature is being disabled from the next release. |                                |

|      | JVM Properties        | View the Java Virtual Machine Properties.                                                                                                 |                                |

|      | Zoom In               | View a smaller part of the diagram in the screen view.                                                                                    | Ctrl+Shift+<br>Equal<br>Symbol |

|      | Zoom Reset            | Reset the screen view to the original size.                                                                                               | Ctrl+M                         |

|      | Zoom Fit              | Fit the content of the block diagram into the viewable page.                                                                              | Ctrl+Shift+<br>Minus<br>Symbol |

|      | Zoom Out              | View a larger part of the diagram in the screen view.                                                                                     | Ctrl+Minus<br>Symbol           |

|      | Full Screen           | Hide the menu and folder bar to display the model to cover the full screen.                                                               |                                |

|      | Undo                  | Last action disappears from the screen.                                                                                                   | Ctrl+Z                         |

| Edit | Redo                  | Repeats your last action.                                                                                                                 | Ctrl+Y                         |

|      | Cut                   | Removes the selection from the active file and places it on the clipboard.                                                                | Ctrl+X                         |

|      | Сору                  | Copies the selection to the clipboard.                                                                                                    | Ctrl+C                         |

| Menu  | Sub Menu            | Explanation                                                                                                                                                                     | Shortcut |

|-------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|       | Paste               | Inserts the selected contents to the clipboard.                                                                                                                                 | Ctrl+V   |

|       | Send to Back        | When the blocks are overlapped, select the required block, and click Send to Back to place the block behind the adjacent block.                                                 | Ctrl+B   |

|       | Bring to Front      | When the blocks are overlapped, select the required block and click Bring to Front to place the block in front of the adjacent block.                                           | Ctrl+F   |

|       | Edit Preferences    | Used to define graphical and model-level properties. Currently there are only a few properties predefined.                                                                      |          |

|       | Find                | Search for a keyword among the model blocks, parameters, expression, and memories.                                                                                              |          |

|       | Automatic<br>Layout | Rearranges the layout of the blocks, connectivity, and relations in the model. DO NOT USE. THIS IS A PROTOTYPE                                                                  | Ctrl+T   |

| Graph | Save in Library     | Saves the current block diagram as a Library. The model must be saved for this feature to be used.                                                                              |          |

|       | Import Library      | Open an XML file containing the list of library items and add it to the Folder structure on the left. The current version does not remember the update when the tool is closed. |          |

| Menu | Sub Menu              | Explanation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Shortcut |

|------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

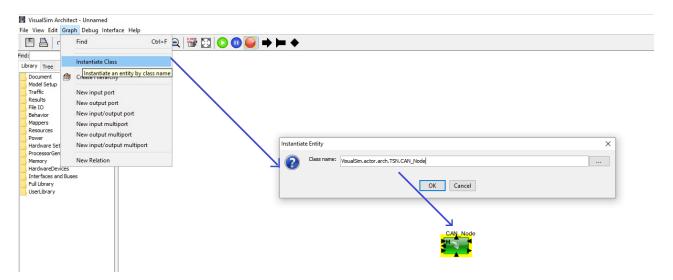

|      | Instantiate Class     | Select the class file to be placed in the BDE. This can be a Java class or an XML class. Use the File Selector to select the file. The file must be located in a directory that is within the CLASSPATH. <b>Example</b> : VisualSim.actor.lib.AbsoluteValue                                                                                                                                                                                                                                         |          |

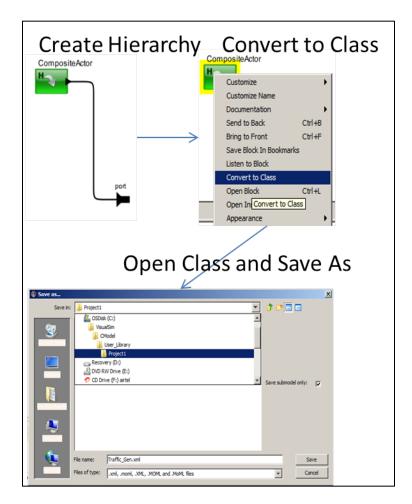

|      | CreateHierarchy       | Select the blocks, connections, and parameters and create a Hierarchical_Block.  Note: All parameters that are used in the selected blocks must be included in the selection; else multiple errors are generated. In some cases, the creation may have errors.  All the connected wires must be selected or the input/output ports for this hierarchical block will be generated automatically. All the created ports are consolidated at the top-left of the screen within the hierarchical block. |          |

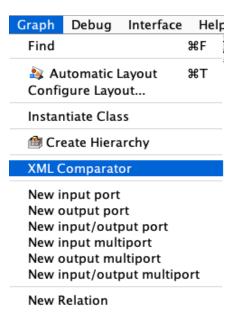

|      | Xml Comparator        | Compares the current Model with another model file.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

|      | New input port        | Places an input port in the BDE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

|      | New output port       | Places an output port in the BDE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

|      | New input/output port | Places an input/output port in the BDE.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| Menu      | Sub Menu                   | Explanation                                                                                                                                                                                                                        | Shortcut |

|-----------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|           | New input<br>multiport     | Places an input multiport in the BDE.                                                                                                                                                                                              |          |

|           | New output<br>multiport    | Places an output multiport in the BDE.                                                                                                                                                                                             |          |

|           | New input/output mulitport | Places an input/output multiport in the BDE.                                                                                                                                                                                       |          |

|           | New Relation               | Places a Relation (black diamond) in the BDE.                                                                                                                                                                                      |          |

|           | Listen to<br>Simulator     | This is a dialog window that is linked to the Digital Debug setting of the Digital Simulator. This displays the block activity and usage statistics.                                                                               |          |

| Debug     | Animate<br>Execution       | Set time to view the dynamic operation of the system model. S Model is animated by highlighting the executing block.                                                                                                               |          |

|           | Stop Animating             | Turns-off the animation.                                                                                                                                                                                                           |          |

| Interface | Generate<br>Wrapper        | This is used with the C, Application Interface, SystemC, and Verilog links. This generates the required code files to interface with the third-party code and simulator. A single selection generates a wrapper for all the links. |          |

| Menu | Sub Menu       | Explanation                                            | Shortcut |

|------|----------------|--------------------------------------------------------|----------|

|      | Compile        | This goes through a sequence to compile the            |          |

|      | Wrapper        | code generated by "Generate Wrapper" along             |          |

|      |                | with the user code. A single selection compiles        |          |

|      |                | all the blocks that have wrappers generated.           |          |

|      | Export to Html | This Menu item enables the user to open any model      |          |

|      |                | and generates an html document. The tool               |          |

|      |                | generates a separate page for each Hierarchical        |          |

|      |                | level. The page contains all the parameters, images,   |          |

|      |                | blocks, and any documentation described using          |          |

|      |                | Annotations. At the bottom of each page, the Applet    |          |

|      |                | containing the model is included. On the top page of   |          |

|      |                | the model, the simulation is executable. For all other |          |

|      |                | pages, the view of the model alone is provided. When   |          |

|      |                | this export occurs, a separate html page is created    |          |

|      |                | for each Hierarchical block. The model that shows on   |          |

|      |                | these pages will not simulate. The top-level BDE that  |          |

|      |                | is exported will have the simulation ability.          |          |

|      |                |                                                        |          |

| Help | About          | View a brief description about the company             |          |

|      |                | and product.                                           |          |

|      | Help           | Opens the starting page of the documentation.          |          |

|      |                |                                                        |          |

|      |                |                                                        |          |

# 3.1.2 Details of Menu and Toolbar Operation

# 3.1.2.1 Open a New Window

# (Includes Block Diagram, Icon Editor, Expression Evaluator, TCL Evaluator, and Text Editor)

- 1. In your Mirabilis Design VisualSim program, click File > New.

- 2. From this menu, select the window of choice Block Diagram, Icon Editor, Expression Evaluator, TCL Evaluator or Text Editor.

- 3. A new window is displayed.

## 3.1.2.2 Existing Window (Model, Hierarchical Block, and URL)

In your Mirabilis Design VisualSim program, click File, and then click either Open File or Open URL.

#### For a File

- a) In the **Look in** list, click the drive, folder, or Internet location that contains the files.

- b) In the folder list, locate and open the folder that contains the file.

- c) Select the file, and then click **Open**.

## For a URL

- a) In the text window, type the full path to the Internet location.

- b) Click OK.

In addition, quick keys can be used:

- 1. CTRL+O To open a file.

- 2. CTRL+U To open an Internet location.

#### 3.1.2.3 To open recently opened models – Recent Files

You can select from a list of most recently saved models.

## 3.1.2.4 Saving Options (Model, Block Diagram, FSM, and Text Editor)

- To quickly save a document, click Save on the Standard Toolbar or CTRL+S or click File and then click Save.

- 2. To save the models in a different location, use the procedure below.

- a. On the File menu, click Save As.

- b. In the File name box, enter a new name for the file.

- c. Click Save.

## 3.1.2.5 Editing Options (Model, Block Diagram, FSM, and Text Editor)

To move or copy a single item:

- 1. Select the item you want to move or copy.

- 2. Do one of the following:

- ⇒ To move the item, click Cut on the Standard toolbar.

- ⇒ To copy the item, click Copy on the Standard toolbar.

- 3. If you want to move or copy the item to another document, switch to the document.

- 4. Click where you want the item to appear.

- 5. Click Paste on the Standard toolbar.

#### Alternate methods:

Use the Cut, Copy, and Paste functions in the Edit Menu.

Reference Guide - 30 - 2003-2022

Use Cut (CTRL+X), Copy (CTRL+C) and Paste (CTRL+V).

To undo or redo an operation on a model:

1. Click undo or redo in the Edit Menu or from the Toolbar.

To delete a block or link:

- 1. Select the block, state, link or transition you want to delete.

- 2. Press DELETE on keyboard, or click Delete or on the Edit menu, click Delete.

#### 3.1.2.6 Zoom In or Out of a model

- 1. You can "Zoom In" to get a closer view of the model or FSM or "zoom out" to see more of the hierarchy at a reduced size.

- 2. Click **Zoom In** and **Zoom Out** on the standard toolbar.

- 3. In addition, you can **Zoom To Fit** to view the entire model or FSM on the screen.

- 4. Click **Zoom To Fit** on the standard toolbar

- 5. Finally you can also **Zoom Reset** to bring the view back to the previously saved state.

- 6. Click the **Zoom Reset** on the standard toolbar.

- 7. In addition to the standard toolbar option, you can also click **View** on the Menu and select the item.

- 8. Finally, you can also use the shortcut keys Zoom in (CTRL+SHIFT+=), Zoom Out (CTRL+-), Zoom Reset (CTRL+=), and Zoom to Fit (CTRL+F) to achieve the same result.

#### 3.1.2.7 Stop and Resume

The simulation can be executed from the BDE window also. These operations are similar to the operations in the Simulation Cockpit:

Reference Guide - 31 - 2003-2022

- ⇒ Click **GO** to start the simulation.

- ⇒ Click **STOP** to terminate the simulation and not continue further.

- ⇒ Click **PAUSE** to temporarily halt the simulation.

- ⇒ Click **RESUME** to restart the simulation from the point where it was paused earlier.

The simulation can be stopped at any time. The displays can be viewed. The simulation can be resumed from that point forward.

#### 3.1.2.8 Editorial Functions

VisualSim provides the following Editorial functions:.

Automatic Layout: This modifies the layout of the blocks and parameters in the current window. Do not use this feature as it incorrectly applies the layout for certain types of models.

Find: Search for a word among all the items in the model including the block names, expressions, parameters, memories, and annotations. This does not find the keyword in class files.

Import a Library: If you want to import a library acquired from another install of VisualSim or hand coded XML file, select Import Library from the Graph menu. Now, select the XML file.

Save in Library: The current model and its entire hierarchical list can be saved in the local library as a block. This is done by clicking the "Save in Library" on the Graph Menu.

Create Hierarchy: A section of the current window can be made into a hierarchical block by selecting the set of blocks and the relations and clicking "Create Hierarchy" in the Graph Menu. This function creates a new block with all of these selected blocks inside. All the required port for the interfaces are automatically created. It is important to select the links connected to the ports at the periphery of the area selected. This ensures that the correct ports are generated.

Instantiate Entity: This instantiates a sub-model or class as a block in the BDE window.

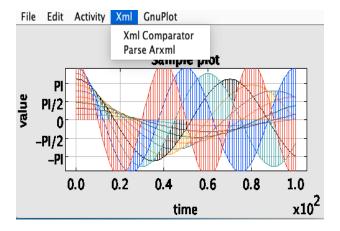

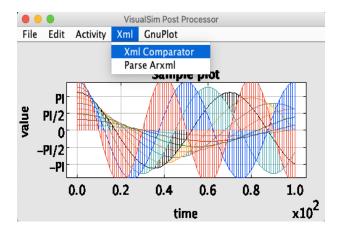

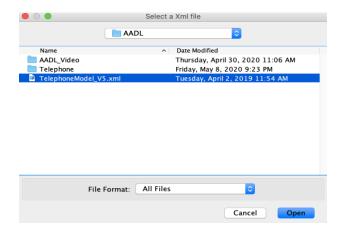

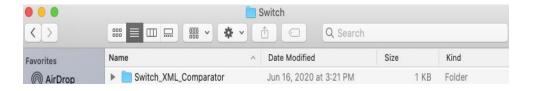

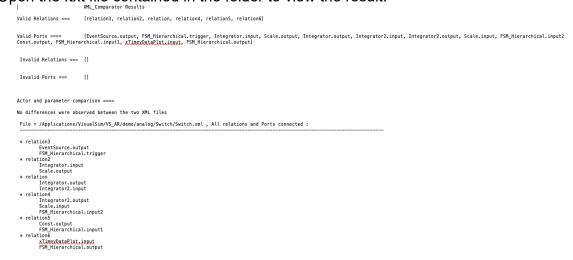

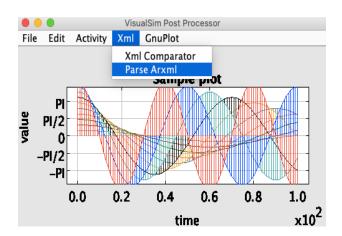

## 3.1.2.9 Xml Comparator

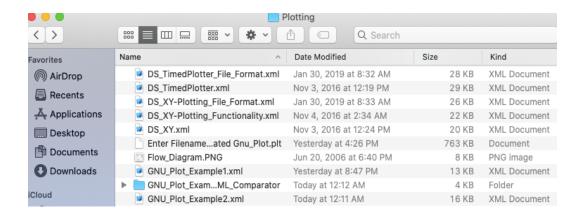

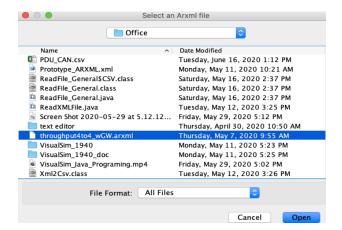

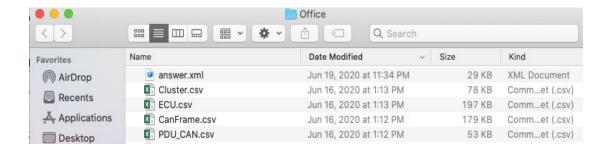

Xml Comparator can be used to compare two model XML files. The user selects a second mocel xml file to compare with the current open model file. The results of the comparison are stored in the same folder as the model with the name- nameofModelFile XML Comparator.

NOTE: A file path or file name containing should not be selected for comparison. If selected, an Illegal Action Exception will be thrown.

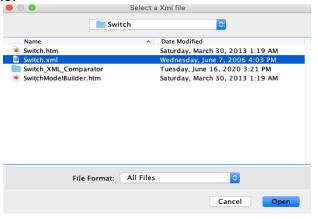

## Steps to perform the comparison

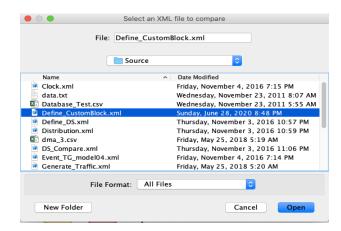

Select the Xml Comparator for the Graph menu.

Select another xml file for comparison.

- Go to the location of the Model xml file.

- Go into the parent folder created in the location.

Open the .txt file contained in the folder to view the result.

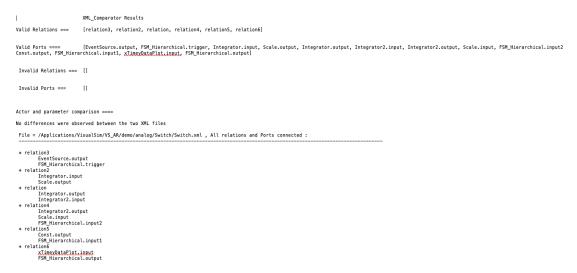

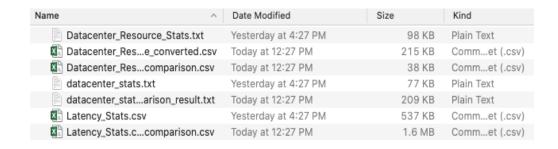

Figure 1

Figure 1 shows the result of the comparison between VS\_AR/demo/analog/Switch/Switch.html with VS\_AR/demo/AADL/TeleModel\_VS.xml.

Figure 2

Figure 2 shows the example of a Model xml file.

## 3.1.2.10 Model Hierarchy:

The model hierarchy can be viewed in two ways.

- ⇒ Click the Tab on the left that says Tree. You can now select and view any Hierarchical block in the model.

- ⇒ Click the icon to see more details about inside of each hierarchical block.

- ⇒ You can drag and drop entities from the hierarchy diagram on to the canvas.

- ⇒ Click the or icons to see the characteristics of the entity.

#### 3.1.2.11 Find

This resides about the Library folder list. This is used to search all the blocks in the library folder list.

## 3.1.2.12 System Properties

To view the system properties, click View in the Menu, and then click JVM Properties.

## 3.1.2.13 System Functions

#### Compile and Generate Wrapper in ModelBuilder

The Generate Wrapper option generates all the required interface blocks to construct a VisualSIm block out of existing Custom C, Custom C++, SystemC, and Verilog wrapper. A note on the Command-line indicates that the operation has completed.

The Compile option compiles all the custom-coded block in the model. Current support is for C, C++, SystemC, and Verilog. The output window indicates when the compile is completed.

#### Memory Management or Garbage Collect

**Operation**: Select the Garbage Collect icon ( ) in the standard toolbar.

**Details**: This is useful when there are custom-coded blocks. Use the Garbage collection at regular intervals and before starting a simulation.

#### Export to Html

**Operation**: Generate a document from the model.

**Details**: This Menu item enables the user to open any model and generate a html document. The tool generates separate pages for each Hierarchical level. The page contains all the parameters, images, blocks, and any documentation described using Annotations. At the bottom of each page, the Applet containing the model is included. On the top page for the model, the simulation will be executable. For all other pages, the view of the model alone is provided.

### 3.1.2.14 Open the Containing Model

Click on the big triangle ▲ in the toolbar to open the hierarchy window containing the current block diagram.

#### 3.1.3 Listeners

- Listen to Block: Right click the required block and select Listen to Block. The Pop up text window displays the progression of execution in the block. Then run the model. This feature is not available for Hierarchical blocks and instantiated hierarchical classes. If you need to see the details of operation within a Hierarchical block, you need to Open Block and select the block to view the execution details. If you need to view the detailed operation of a Instantiated class, you need to select Open Instance and select the block to view the execution details.

- Listen to Port: Right click the required port and select Listen to port. The Pop up text

window displays each Token passing through the port. This feature is not available for

Hierarchical blocks. It is supported for regular blocks and instantiated hierarchical classes.

If you need to see the data flowing into and out of a Hierarchical block, you could add a

"relation" in front of the port. You can connect a Text\_Display to this relation to view the activity.

#### 3.1.4 Folders and Tree

**Folders:** The list of pre-built and user library are provided in the Library folder on the left-side of the Block Diagram Editor. Click on any of the names to see the library blocks listed below. To use a block, simply select the block name in the Library and drag-n-drop the block into the Editor space.

**Tree:**The Tree tab allows the user to view the list of Hierarchical blocks in the model. The user can click on a name and the respective hierarchical block opens. After the block is open, go back to the original Window, select, and drag-n-drop the hierarchical into the canvas.

**Find:** The Find function in the Folder can search the entire library table and find the block that matches the search word. Currently this only searches for an exact match.

### 3.2 Text Editor and Listener Windows

### 3.2.1 Introduction

The text editor is used extensively for authoring code in the Script. It is also used to view text files. The Listener windows use the Text Editor. So, all the commands listed below are supported by those viewers also.

### 3.2.2 Commands

All the File, View, and Help commands match the Block Diagram Editor.

# 3.2.3 Quick Key Commands

The Text Editor does not have the Menu Bar. The user will have to know that CTRL+C, X, V, CTRL+F,H, R are for copy, cut, paste, find, forward, and backward.

### 3.3 Plotters and VisualSim Post Processor

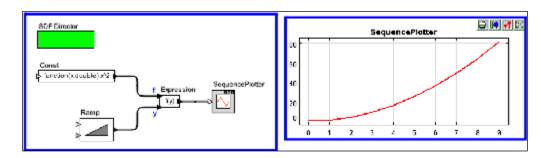

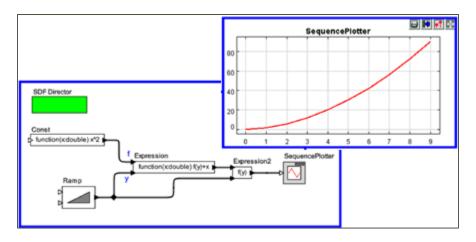

#### 3.3.1 Introduction

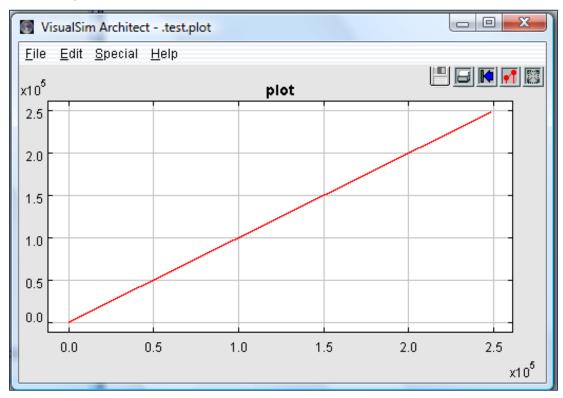

VisualSim Plot provides comprehensive charting and analysis capability that enables the modeler to remain within the VisualSim environment for all complex analysis. The Plot graphs are instantiated in a model and are displayed as independent viewers when a simulation is started. The independent Post Processor application allows the user to set the view vs. save options for the plots and the plot file name. An associated index file allows for the plots from multiple runs to be combined and viewed in a single display. The graphs can be generated using various Display blocks in VisualSim and by importing XML data files from an external source. The graphs can also be embedded in an HTML executable specification as a Java Applet. Plot includes all the format functions required to modify the view. A variety of charts including, XY, bar, histogram, timeline, and signal are available.

VisualSim Plotting is a set of two-dimensional signal plotters that enhance the capability of the VisualSim simulation platform. Plotting is sometimes viewed as a "post" modeling activity. You can use the VisualSim Post and the Post Processor application to graphically display and analyze data collected from the simulation. The Plotters can organize results into a variety of x-y graphs and histogram plots for graphical display. An XML extension language for plot data has been created and is available for the user to extend.

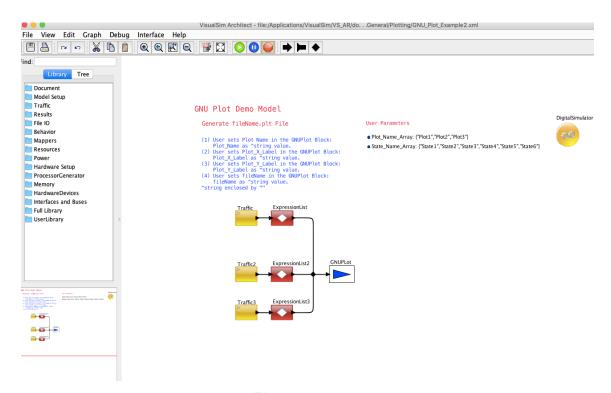

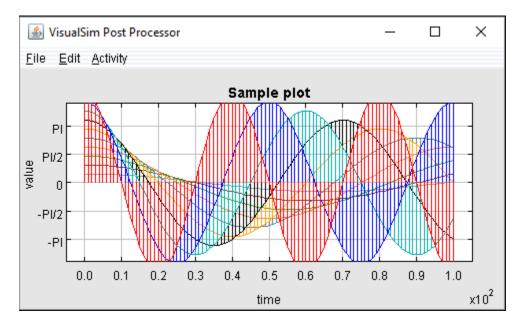

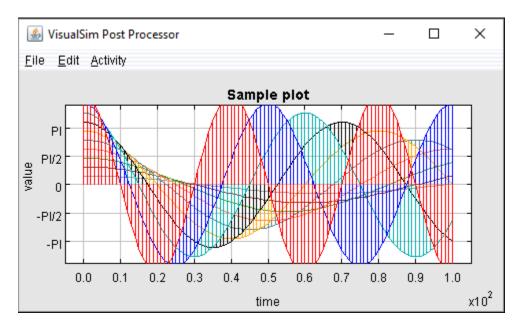

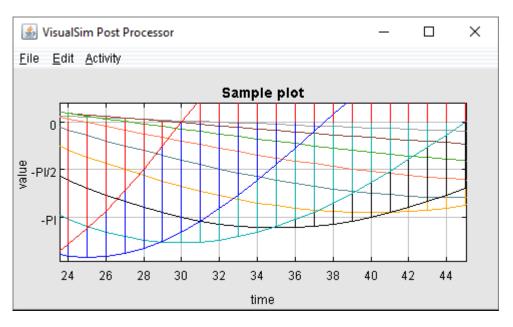

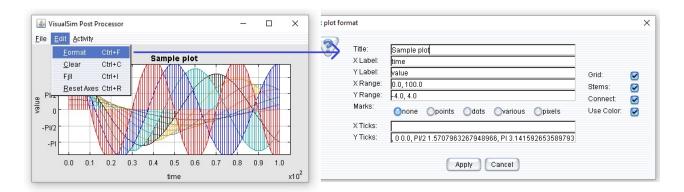

Figure 1. VisualSim Plot Application Window

The following are the key properties of the product:

- Embeddable in applets or applications

- Auto-ranging

- Automatic or manual labeling of axes

- Automatic or manual tick marks

- Logarithmic axes

- Live, animated plots

- Zooming upto the resolution

- Various plot styles: connected lines, scatter plot, bars, and so on

- Various point styles: none, dots, points, and unique marks

- Multiple data sets and a legend

- Color or black and white plotting

- Error bars

- Editable plots

- XML language for specifying plots

- Within a folder if there are multiple files having same name with consecutive numbering like myfile\_1, myfile\_2, myfile\_3, then on selection, all 3 plots will be combined into a single plot and thus a single metric can be compared for different test cases easily.

# 3.3.2 Post Processor Window

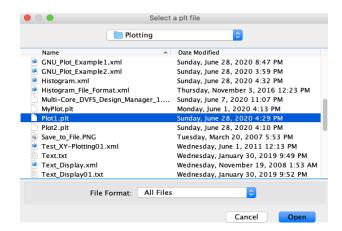

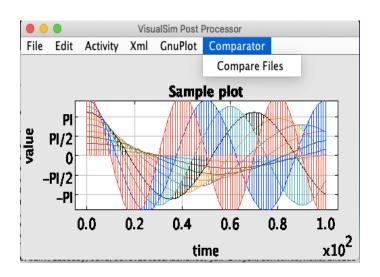

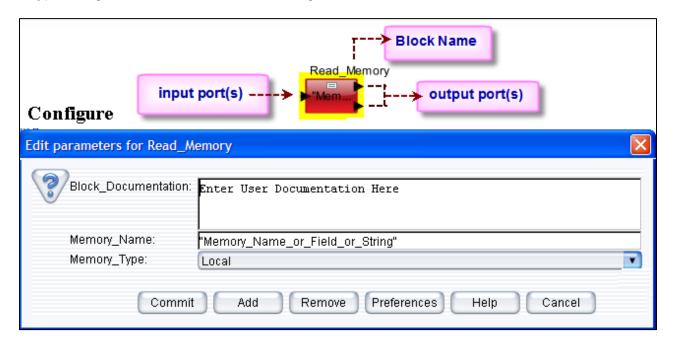

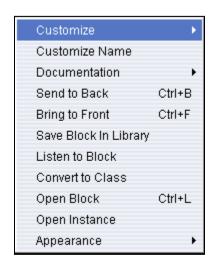

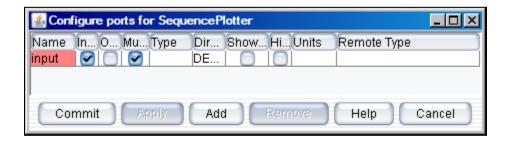

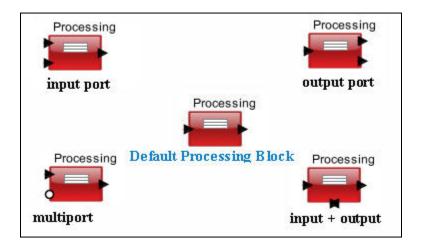

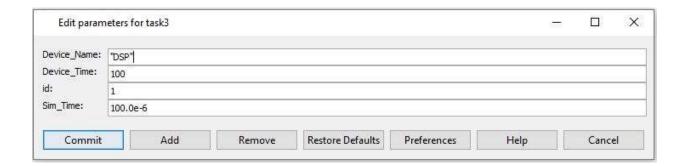

| File    | Same as Block Diagram Editor. Note that Print, Export, and Import are disabled. |                                                         |  |