The global semiconductor industry is rapidly embracing chiplet-based architectures, heterogeneous integration, high-bandwidth die-to-die fabrics, and system-level co-design. As design complexity increases, engineering teams across compute, networking, AI accelerators, RF, memory, and advanced packaging are demanding faster ways to explore architectures, evaluate trade-offs, and validate system performance before any RTL or silicon investment.

At this year’s Chiplet Summit—held on February 17–19 at the Santa Clara Convention Center—Mirabilis Design will demonstrate how system architects and semiconductor designers can accelerate innovation with VisualSim Architect, the industry’s most comprehensive system-level modeling and architecture-exploration platform.

Exhibits: Booth 314- Ask for Kesudh, Pavan, Vaish or Deepak

Paper Presentations

| Deepak Shankar | MIRABILIS DESIGN | H-103: Design – 3 | Wednesday | 5:00 PM |

| Tom Jose | MIRABILIS DESIGN | A-201: Design – 4 | Thursday | 9:00 AM |

| Mohan Dhene | QUALCOMM | F-201: Die-to-Die Interfaces – 5: High-Frequency Applications | Thursday | 9:00 AM |

Forums

| Deepak Shankar | MIRABILIS DESIGN | Electronic Design Forum | Wednesday | 4:10 PM |

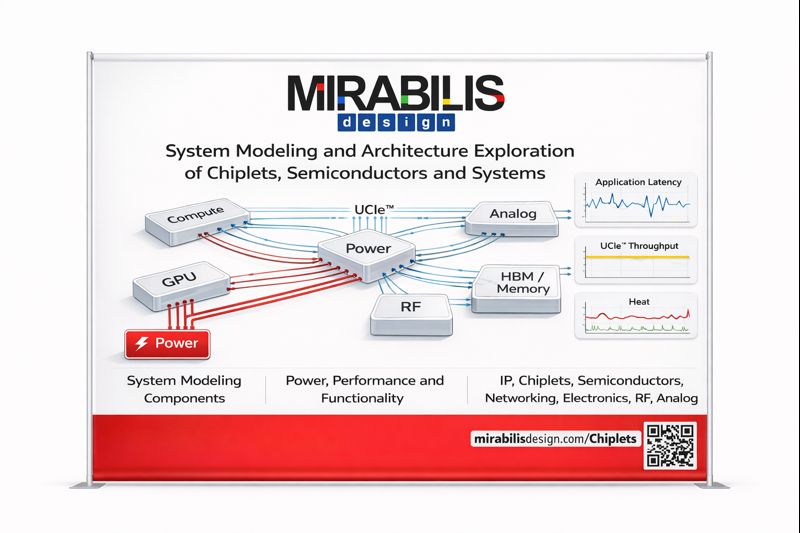

Below is a preview of the graphic featured at our booth. It illustrates how VisualSim Architect models Compute, GPU/AI/NPU, Analog, RF, and HBM/Memory chiplets connected through UCIe and OCP Bunch of Wires, with integrated power delivery, latency, throughput, heat, and runtime power plots—all generated from real system-level simulation.

UCIe (Universal Chiplet Interconnect Express)

Component

Architecting for Efficiency: Measuring and Managing Power from Chiplet to System

Blogs

Power defines performance. Join Mirabilis Design on November 6 2025 in a Webinar to see how VisualSim Architect lets system architects explore, measure, and optimize power at every stage of design. Speakers: Deepak Shankar, Founder & Chief Technologist, Mirabilis Design Inc. LinkedIn Profile Overview Across the globe, data centers and high-performance computing systems are now measured by […]

Architecture Exploration of ARM-based SoC and Chiplets

Blogs

Unlocking Optimal Power and Performance: A Deep Dive into ARM SoC Modeling In the competitive world of semiconductor design, balancing power consumption with high performance is a constant challenge. With VisualSim Architect, engineers can simulate intricate ARM-based SoCs with unparalleled accuracy, paving the way for innovative, power-efficient solutions. The Future of SoC Design: As the […]

Standards-Based Chiplets vs. Proprietary Designs

Blogs

Standards-Based Chiplets vs. Proprietary Designs: A Technical Perspective The rapid rise of chiplets has sparked a debate between standards-based architectures and proprietary designs. Both approaches have their merits, and the choice often hinges on specific application requirements. Proprietary Chiplets: Tailored Precision Proprietary chiplets are custom-designed for specific use cases, offering highly optimized performance and features. […]

Chiplet: Redefining Modular Semiconductor Architectures

Blogs

Chiplet: Redefining Modular Semiconductor Architectures The semiconductor industry is at a critical juncture, facing unprecedented demand for high performance, reduced costs, and faster time-to-market. Enter chiplets: a groundbreaking approach that breaks down complex monolithic chips into modular, reusable blocks. This innovative design paradigm offers unparalleled flexibility and scalability, making it a cornerstone of next-generation computing. […]

Why Chiplets Have Become Essential in a Post-Moore’s Law World

Blogs

Chiplets Have Become Essential in a Post-Moore’s Law World For a generation of engineers, Moore’s law has proved to be a constant. The industry has continued to advance forward year after year with the promise of performance gains holding steady. That is until recently. With Moore’s law at least slowing (if not outright failing) and […]

July 2025: Driving Innovation: VisualSim Hits the Road, the Classroom, and Industry

Blogs

Mirabilis Design Newsletter 2025 Founder’s Note I hope you’re enjoying a wonderful summer! At Mirabilis Design, AI is taking center stage — helping us track dynamic behavior during simulation and detecting performance bottlenecks, thus maximizing the role of system modeling. By integrating VisualSim into the broader EDA workflow through co-simulations and more parameters for system components, we’re […]

Optimizing Automotive Electronics Architecture for Autonomous and Electric Vehicles Using System-Level Modeling

Blogs

Author: Deepak Shankar, Vice President Technology, Mirabilis Design Inc. Introduction The rapid adoption of autonomous driving technologies and electric vehicles (EVs) has fundamentally shifted automotive electronics design. As AI-based functionalities proliferate across vehicle subsystems, system architects face increasing complexity in balancing performance, power efficiency, and hardware costs. Traditional design approaches relying on spreadsheets and analytical […]

ARM-Based SoC Design: Mastering System-Level Modeling

Blogs

Revolutionizing ARM-Based SoC Design: Mastering System-Level Modeling with VisualSim Architect The semiconductor landscape is evolving at an unprecedented pace. In an era where ARM-based SoC dominate high-performance computing, efficient system-level modeling has become crucial for experimenting and optimizing superior performance and power optimization. Enter VisualSim Architect—a tool that offers the only architecture models for ARM […]

ARM corelink, Arteris NoC, UCIe, Bunch-of-wires, CXL and PCIe

Blogs

ARM CoreLink, Arteris NoC, UCIe, Bunch-of-Wires, CXL, and PCIe – Designing the Interconnect is Not for the Weak-Hearted! In today’s high-stakes world of System-on-Chip (SoC) design, figuring out the best interconnect architecture can feel like navigating a maze. With so many choices—ARM CoreLink CMN700, Arteris FlexNoC, UCIe, Bunch-of-Wires, CXL, and PCIe—it’s easy to feel overwhelmed. […]

Webinar: ARM corelink, Arteris NoC, UCIe, Bunch-of-wires, CXL and PCIe

Blogs

ARM corelink, Arteris NoC, UCIe, Bunch-of-wires, CXL and PCIe – Designing the interconnect is not for the weak-hearted! Timings: Session 1: 11:30 AM India / 3:00 PM Japan or Korea / 2:00 PM China Register here: https://bit.ly/4elxVwY Session 2: 10:00 AM PDT / 1:00 PM EDT Register Here: https://bit.ly/4epEQ8v With so many Network-on-Chip (NoC) solutions […]

Digital Twin | AI-drives Visual Picture of the Power Flow

Blogs

AI-drives Visual Picture of the Power Flow at Architectural Stage of Design Design community has fully embraced Computer Aided Design(CAD) and Electronics Design Automation (EDA) tools for system design, however system modeling is one of the area, where some of the product design experts are not fully aware of high value (beneficial /shift-left) tools in […]