Stochastic models are constructed to gain a better understanding of the whole system which would not otherwise be possible with analytical methods. Refinement models are done for potential problem areas to explore in detail. For example a higher level of abstraction/statistical level mean it is modeled at the transaction level. Such models will have an accuracy range of 60% to 80% for functionality and 80% for the transaction flow to the element being investigated. 75% to 80% accurate traffic profile with a detailed processing element is sufficient to make valuable design decisions on peak utilization, throughput, or latency.

Abstract model provide an insight into system in an entirely different light. In terms of innovation, thinking along parallel, but separate lines of thought, can provide insight into a system that was otherwise hidden in the details.

Statistical level of modeling is the right choice if the user is doing first level of system sizing to complete system architecture.

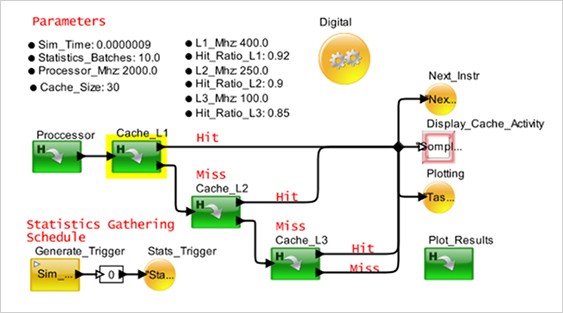

Figure 19 is an example statistical processor based system with three levels of cache hierarchy. The Statistical process is actually a traffic which generates statistical stream of instructions based on the processor speed. The Statistical cache hierarchical block accepts cache requests and it delays the request based on the instructions defined, and also it checks for the cache hit and miss ratio to transfer the control to other blocks for further processing.

Hardware level model

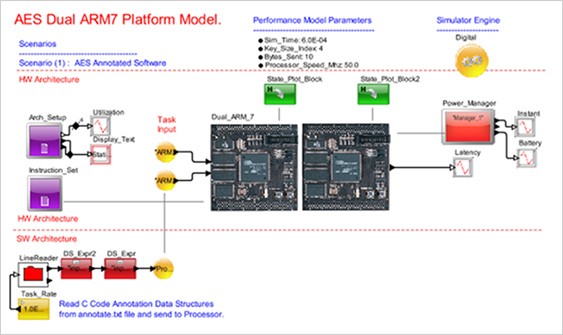

Architecture models of the hardware, software, network and RTOS are constructed to determine the system impact of selecting a technology. Accuracy range of Hardware level models are of 80% to 95% based on the level of details at which model has been developed.

Figure 20 is an example hardware level accuracy model which is developed using prebuilt library blocks which are timing and functionally accurate. At this level of modeling the selection of a standard such as PCIe vs RapidIO or LPDDR vs DDR3 is performed. Moreover this methodology is good to tune the system attributes at a fairly detailed level of granularity.

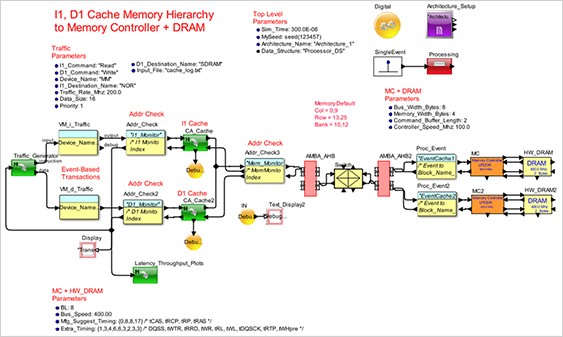

At this level of abstraction, the models will be close in accuracy to the implementation. Also, the address data, control signal and the data movement are modeled in detailed. VisualSim has a large library of cycle-accurate models that have been validated against vendor timing diagrams. These models can be used to resolve design options related to interleaving of data in memory, buffer thresholds in buses and timing diagram displaying the sequence of events. The reports are useful to trace bugs in the implementation, and also to provide inputs to the implementation designers on the verification tests.

Figure 21 is a cycle accurate level model with trace file based traffic generator, Cycle accurate cache and AHB bus. The model developed at this level needs the description of eachtransactions. The architecture is fixed at this stage but attributes are still flexible such as DDR3 vs DDR4.

Cycle accurate level model