Power_Perf_example

Browsable image of the model.

- To download OpenWebStart

click on the links -

Windows- Compatibility:Windows 10 or higher (*)

macOS - Compatibility:macOS 10.15 (Catalina) or higher (*)

Linux - Compatibility:Ubuntu 18.04 LTS or higher (*)

- For an executable version,

- Mouse over the icons to view parameters. Click on hierarchy and plotters to reveal content (if provided).

- To simulate, click on Launch button, open downloaded file and click Run on the Java Security Page.

Introduction

VisualSim is a modeling and simulation software used for the architecture exploration of electronics systems, and semiconductors. Using this environment, designers can construct graphical virtual models of their proposed system and conduct performance, power and functional analysis.

This is an example of the performance modeling using a set of standard IP blocks and a custom behavior flow diagram. Purpose of this model is to select the hardware platform for the target MPEG video application. The requirement is processing 13,000 matrices in 20 ms at less than 1 watt of power.

The model has behavior definition, hardware architecture, and the mapping. Hardware platform has ARM 926S, DSP, AHB, AXI, SRAM, Flash, SDARM and Hardware accelerator. Block diagram of the proposed system is as shown in figure below

1. HW architecture constitutes processor, cache, memory, bus and peripheral modules.

2. SW architecture constituting dummy drivers mapped to C code & a real use case with SW blocks as models

3. HW -SW partitioning with appropriate results which show the various tradeoffs done.

Simulation Model

We have defined the behavior definition as a flow diagram and is represented as green blocks at the bottom. Each green blocks represents a specific task of the application. Flow diagram approach of defining the software behavior flow is the most reliable and advantageous in terms of representation and mapping. These tasks are mapped on to the target architetcure defined above, during architecture exploration one can easily modify the combination of mapping tasks on to the hardware architetcure elements to achieve optimal performance and power requirements.

Configuration:

Select the following for different

simulation runs :-

1. Select_Scenario : This selects

whether you want to run the basic application or do HW/SW partitioning

2. Partitioning : Choose SW or HW for the Rotation Algorithm and see results

3. Simulation time : Run

simulation for a longer time to see various plots

4. Every architecure block

is configurable via several parameters like frequency, size etc.

In this model we have

considered 2 different approaches to meet the requirements, one is to process

all applications in software, and the other is to move a few processing-intensive

applications to hardware accelerators to improve the performance.

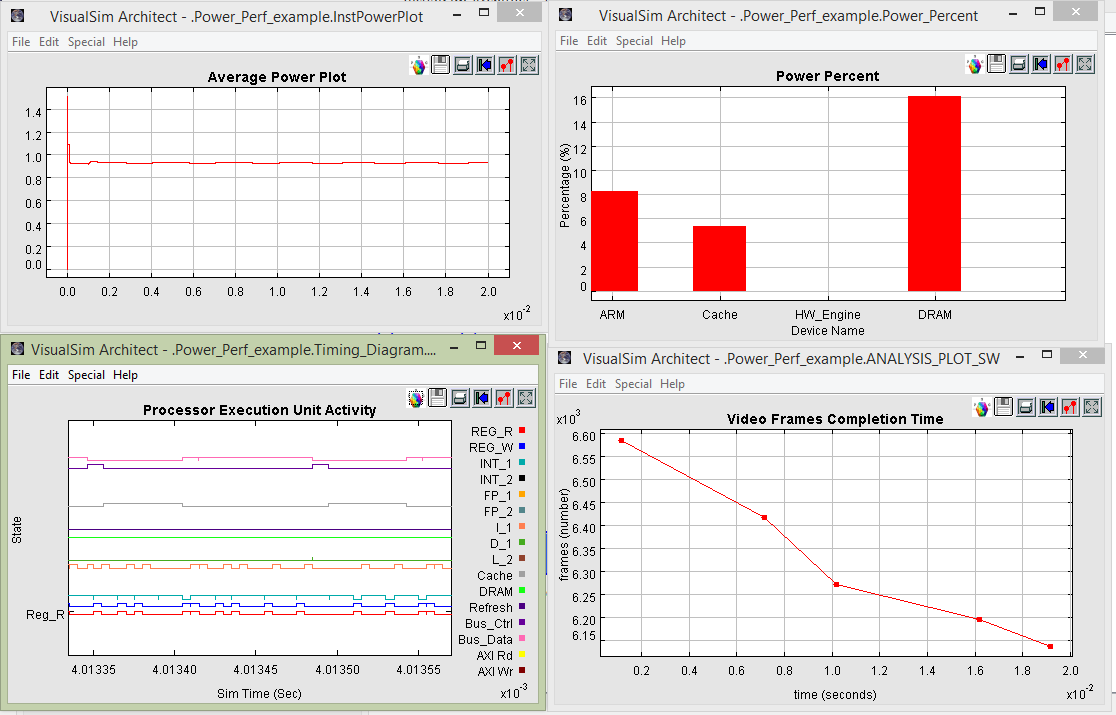

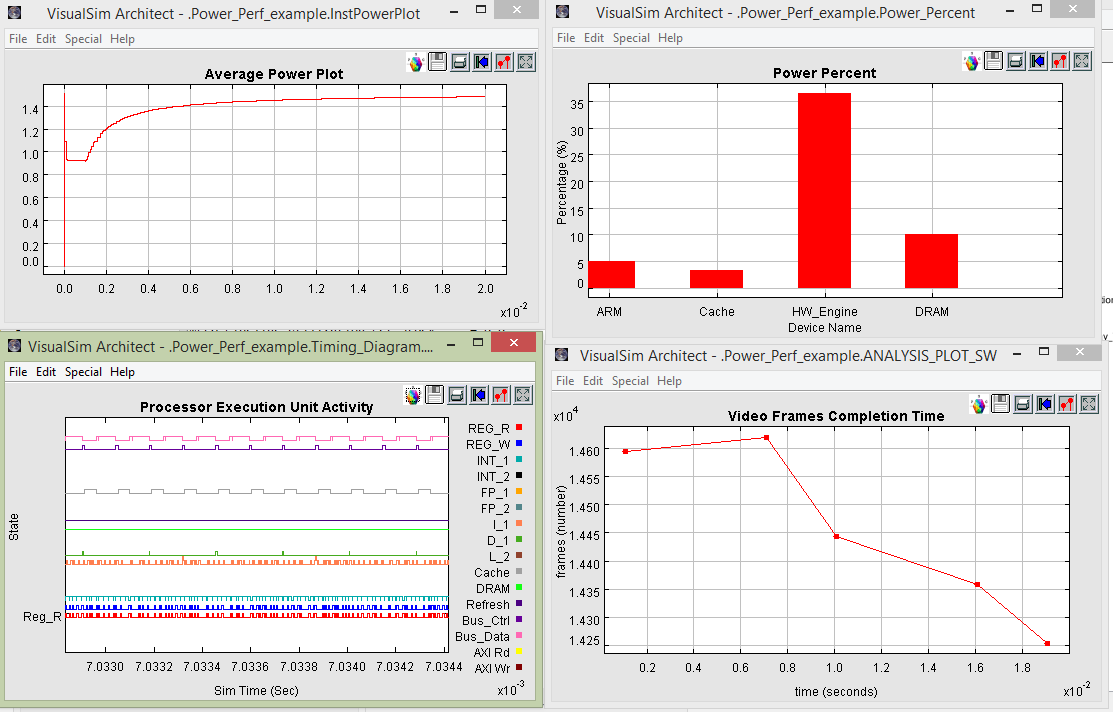

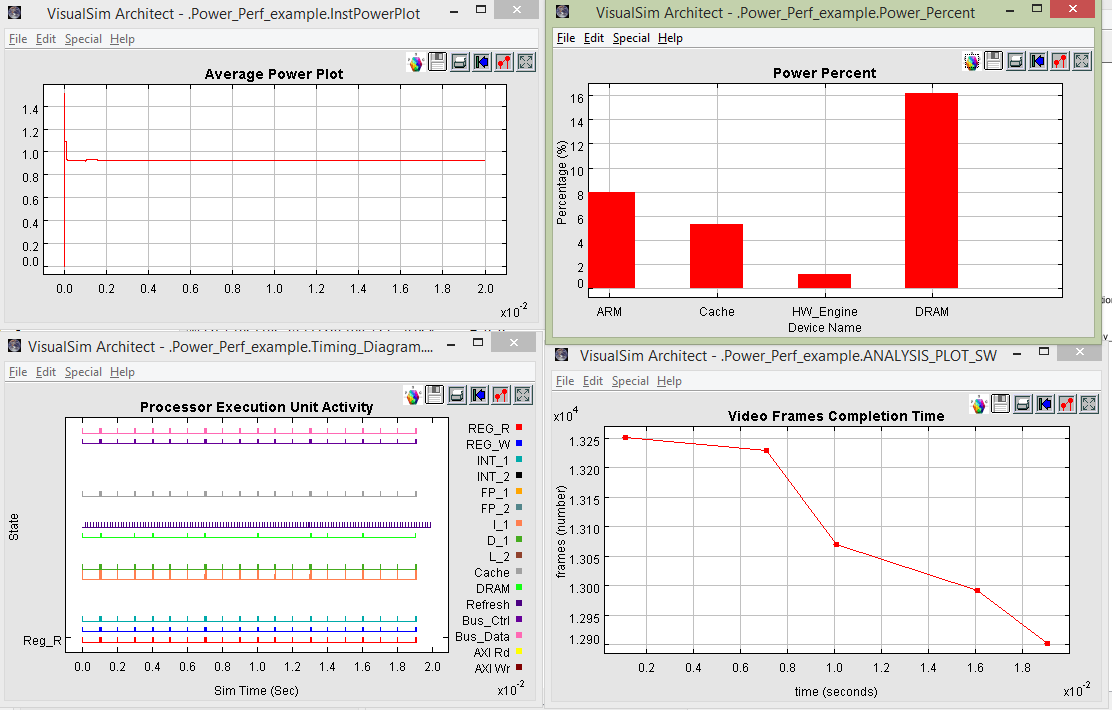

We are expecting about 13K matrices of video frame keeping power consumption under 1 w. Initially run simulations with default settings, make sure that the paarmeter Partitioning is set to SW. The results and plots show that when the tasks are processed in software, we get 6600 matrices in 20 ms and the power consumption is under 1 watt. The power is fine but we do not meet the performance criteria. As we were not meeting the performance requirements while running all tasks on ARM, we found that moving some critical tasks such as rotate frame task on to a accelerator would help us in achieving performance.When we move the rotate frame application to the hardware accelerator by modifying the parameter value "Partitioning" to "HW", the performance improves substantially to 14,000 matrices but power consumption is at 1.6 W. We now introduce power gating for the hardware accelerator by turning it off when not used. To do this set the parameter "Enable_Pwr_Gating" to true. The performance drops to 13,000 matrices but the power consumption is under 1 watt. So, we can see the trade-off.

Results

If the model runs

correctly, the result should look like:

Partitioning with SW IP:

|

Partitioning with HW IP

|

Partitioning with HW IP with Power gating algorithm

|