Abstract

The RISC-V architecture offers unparalleled flexibility in processor design, allowing custom instruction sets, memory hierarchies, and peripheral configurations. This study presents a model-driven approach using VisualSim Architect to explore the performance, power, and functional trade-offs of RISC-V cores in complex system-on-chip (SoC) environments. We simulate multiple RISC-V microarchitectures with configurable pipeline stages, cache hierarchies, interconnect topologies, and memory controllers. By integrating workload-specific task graphs and RTL-accurate IP models, the platform provides early insights into latency, throughput, power envelopes, and system bottlenecks. The framework enables architecture teams to compare base vs. custom extensions, identify optimal core/memory/interconnect ratios, and validate software task mappings. Results show significant savings in design iterations and verification effort by frontloading architectural decisions through system-level modeling.

Keywords: #RISC-V, #VisualSim, #system_modeling, #microarchitecture_exploration, #SoC #simulation, #custom_ISA, #early_power_analysis, #pipeline_tuning, #task_mapping

Introduction

RISC-V’s open and modular nature has catalyzed its adoption in heterogeneous computing platforms. However, its flexibility presents a challenge: How do architects determine the ideal combination of instruction set extensions, pipeline depth, memory subsystems, and system interconnects for their application domain?

This article describes how VisualSim Architect enables rapid and rigorous exploration of RISC-V architectural choices at the system level. By leveraging a high-fidelity, executable modeling environment, hardware designers can make data-driven decisions before RTL development begins.

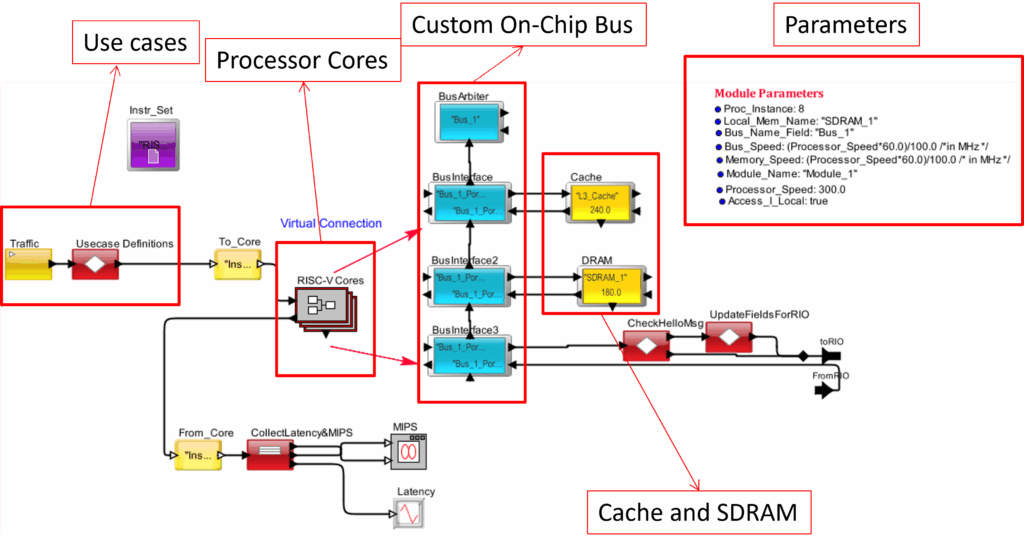

RISC-V Microarchitecture Modeling in VisualSim

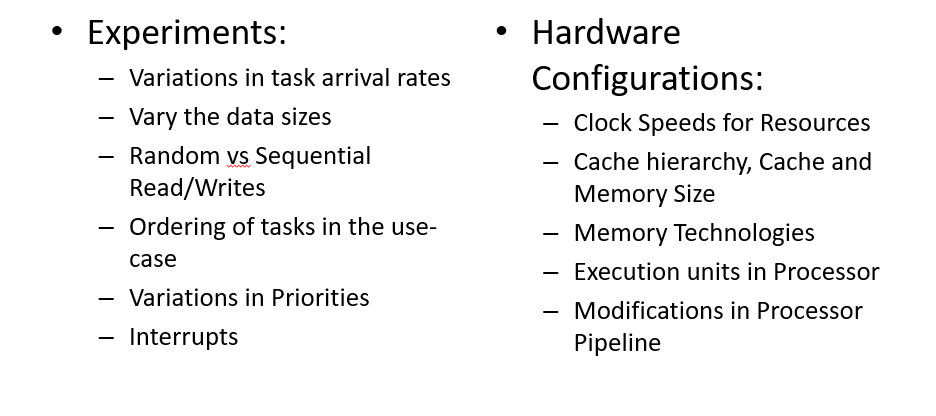

VisualSim provides a drag-and-drop library of prebuilt RISC-V cores, including both scalar and superscalar variants. Users can customize:

- Number of pipeline stages (e.g., 5-stage vs. 7-stage).

- ISA extensions (e.g., RV32I vs. RV32IMAFDC).

- Branch predictors and out-of-order windows.

- Cache hierarchies with shared/private L1/L2s.

- Optional TLB and MMU modules.

Instruction traces or task graphs can be imported to emulate real workloads, and each instruction is executed in a time-accurate manner.

Interconnect and Memory Subsystem Exploration

With Arteris NoC, CoreLink, or custom bus support, VisualSim lets users:

- Connect cores via mesh, ring, or crossbar.

- Adjust bus widths, arbitration, and QoS schemes.

- Analyze congestion and latency paths across multiple hops.

- Co-simulate with LPDDR/DDR controllers and shared memory models.

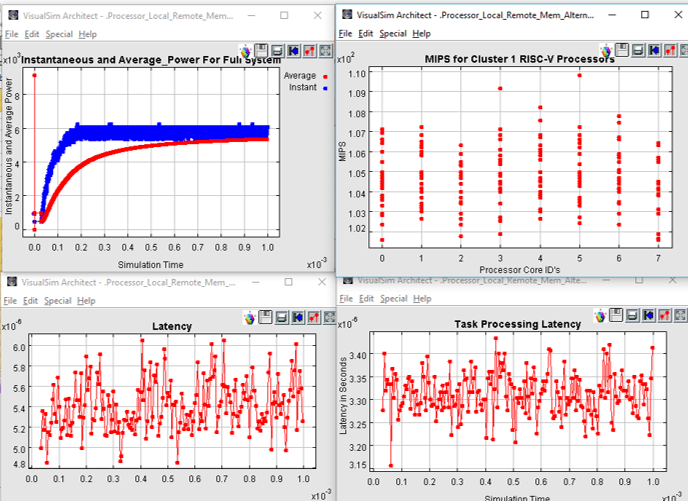

Throughput and latency heatmaps identify bottlenecks in cache coherence or memory controller contention.

Power and Performance Trade-offs

By integrating power libraries or leveraging pre-characterized power profiles, VisualSim enables early energy-per-task analysis. Architects can compare:

- Scalar vs. vector core power envelopes.

- Effect of custom instruction set extensions (e.g., bit-manip or crypto).

- DVFS strategies across heterogeneous RISC-V clusters.

Design Insights

Using VisualSim, customers have:

- Reduced architecture decision time by 40%.

- Eliminated 2–3 iterations of RTL rework.

- Identified optimal trade-offs between area, power, and performance using Pareto analysis.

One case study showed that a custom 6-stage RISC-V core with a shared 256KB L2 and mesh interconnect provided 1.8× performance improvement over a baseline configuration with 15% lower energy per instruction.

Conclusion

VisualSim Architect transforms RISC-V development from guesswork to guided exploration. It offers a unified environment for hardware/software co-design, reducing risk while accelerating time-to-market. Whether designing for automotive MCUs, edge AI, or custom ASICs, VisualSim equips architecture teams to confidently evaluate trade-offs and design the optimal RISC-V SoC.

To learn more, contact [email protected].