AVFS: System Level Modeling

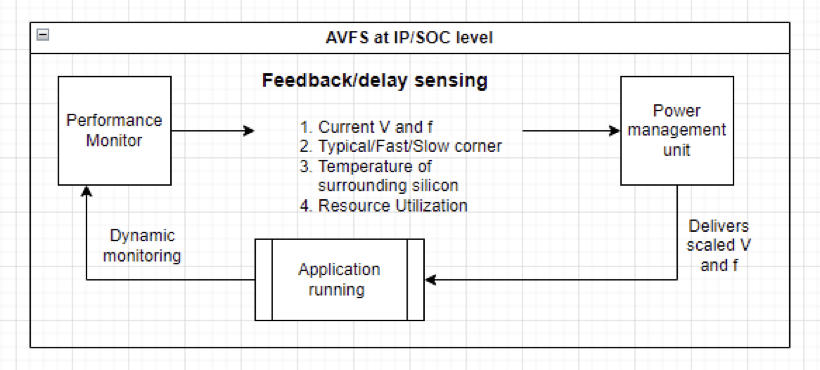

Modern SOCs employ multiple power management strategies either at individual IP level or full SOC level. One such strategy is adaptive voltage and frequency scaling (AVFS).In AVFS, a closed-loop feedback system is implemented between the voltage scaling power supply and delay-sensing performance monitor on the SoC.The on-chip performance monitor not only sees the actual voltage delivered on-chip but also understands whether the silicon is slow, typical or fast, and the effect of the temperature of the surrounding silicon. It can also track the utilization parameters to decide the choice of operating points.

The figure below represents an example of this feedback system between power manager and performance monitor on a chip.

VisualSim can be used to model the effect of power management strategies on the system performance and hence decide on a power-performance tradeoff in early system design phases.

The figure below shows how the model would look in the software.

The below graphs represent the variations being observed in a demo model when a simple AVFS algorithm is used to track the Utilization_Mean of resources.

- Results when AVFS is not enabled

- Results when AVFS is enabled

In case 1, the peak latency is low and the peak power is high since we constantly operate at higher frequency. In case 2, the V and f are being scaled based on Utilization. The power consumption reduces at the cost of performance (end to end latency) .

Based on the choice of V and f , we can further observe the variations in the System latency and power. The results can be used to perform a tradeoff analysis.It can further be extended to try out various levels of AVFS algorithms in terms of aggressiveness, model the effects of overhead delay etc.