Hardware-software partitioning is the division of an application’s computations into a part that executes as sequential instructions on a microprocessor (the “software”) and a part that runs as parallel circuits on some IC fabric like an ASIC or FPGA (the “hardware”), to achieve design goals set for metrics like performance, power, size, and cost. The circuit part commonly acts as a coprocessor for the microprocessor.

HW/SW partitioning is an important development step during HW/SW co-design to ensure application performance in embedded System-on-Chip (SoC). The partitioning is done in the earliest stages of the design; at the stage where there is the greatest possibility for changes. The hardware software partitioning tries to exploit the synergy of hardware and software.

The classic HW/SW partitioning process includes the system that was immediately partitioned into hardware and software components. The hardware and software are developed separately. The “Hardware First” approach is often adopted. Some of the implications of these features are that the HW/SW trade-offs are restricted. The impact of HW and SW on each other cannot be assessed easily. Consequences of adopting these classic techniques are-poor quality designs, costly modifications and time to market increased. Partitioning has dramatic impact on the cost and performance of the whole system.

The HW/SW partitioning improves overall system performance, reliability, and cost effectiveness because defects found in hardware can be corrected before tape-out. Partitioning benefits the design of embedded systems and SoCs, which need the HW/SW tailored for a particular application.

Some of the key benefits of the HW/SW partitioning are:

- Faster integration – reduced design time and cost

- Better integration – better performance

- Verified integration – lesser errors and re-spin

Some of the important hardware software partitioning applications are in the areas of:

- Consumer electronics

- Telecommunications

- Manufacturing control

- Autonomous driving

HW/SW partitioning involves architectural assumptions like:

- Processor type

- Interface style

- Memory structure

- Availability of resources

The main objectives for partitioning would be speedup, latency requirement, silicon size and cost.

HW/SW partitioning allows several different designs (HW/SW partitions) to be evaluated, aids in determining the best implementation for a system, partitioning applied to modules to best meet design criteria (functionality and performance goals).

Key issues faced during the HW/SW partitioning are the partition algorithm and the hardware software estimation. Multi-core processing is recognized as a key component for continued performance improvements. Single core products are showing a diminishing ability to increase product performance at pace with consumer desire. Therefore the use of multi-core systems becomes essential. Multi-core processing involves complex changes to system and software to obtain optimal performance. Partitioning of these multi-cores is the central challenge of developing a multi-core environment.

Implementing a system in which work can be done in parallel in a computing environment where order must be maintained at all costs, poses problems. Here, partitioning between the multi-cores provide a path forward for increased performance. This part of the designing requires comprehensive and pervasive system and software changes, as well as new and innovative hardware designs to ensure that the software can take advantage of the increased computational power.

Along with this is the use of multi-core IP to be integrated on a single chip. The buses and point-to-point communication architecture is replaced by Network-on-Chip (NoC) in System-on-Chip (SoC). NoC can handle the communication of hundreds of cores and allow several transactions concurrently. The NoC topology not only plays an important role in performance parameters such as area, power consumption, latency, and throughput. Topology describes the arrangement of the cores here. The mesh partition topology is useful when the total area needs to be reduced. Whereas the ring partition topology reduces the average latency. The heterogeneous and hybrid clustered topology is to reduce the average latency, response time, and keeping the area of the topology constant. There will always be a trade-off between the partition topology used and the desired performance metrics. According to the application at hand the designer needs to finalize one of them.

With a single core supporting number of partitions, the architecture is said to be integrated. The reduction in the number of nodes and networks as a consequence of the integration leads to an increase in hardware reliability and a decrease of the hardware cost. An integrated distributed architecture for mixed-Criticality applications must be decided on a core design that supports the safety requirements of the highest considered criticality class.

In VisualSim Architect, the hardware software partitioning can be implemented efficiently, with the model blocks diagram as shown here-

A dedicated scenario for the hardware software partitioning using the rotation algorithm is created. The parameter of ‘select partitioning’ provides the designer the liberty of choosing the desired hardware/software partitioning.

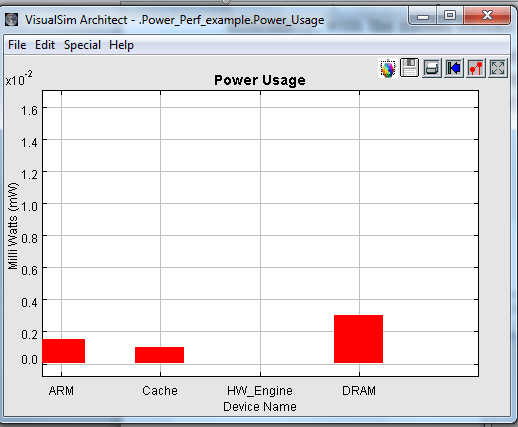

Here, the power usage plot is shown, which mostly between 0.2percent to 0.3 Watts. The designers can further make modifications in the model and get more optimized results.

Have a question? Or you would like to know more?